- Deutsch

-

EnglishDeutschItaliaFrançais日本語한국의русскийSvenskaNederlandespañolPortuguêspolskiSuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикAfrikaansIsiXhosaisiZululietuviųMaoriKongeriketМонголулсO'zbekTiếng ViệtहिंदीاردوKurdîCatalàBosnaEuskeraالعربيةفارسیCorsaChicheŵaעִבְרִיתLatviešuHausaБеларусьአማርኛRepublika e ShqipërisëEesti Vabariikíslenskaမြန်မာМакедонскиLëtzebuergeschსაქართველოCambodiaPilipinoAzərbaycanພາສາລາວবাংলা ভাষারپښتوmalaɡasʲКыргыз тилиAyitiҚазақшаSamoaසිංහලภาษาไทยУкраїнаKiswahiliCрпскиGalegoनेपालीSesothoТоҷикӣTürk diliગુજરાતીಕನ್ನಡkannaḍaमराठी

Verschlossenen des Potenzials der T-Flip-Flop-Konvertierung: eine detaillierte Anleitung

- 2024/07/10

- 826

Erkunden Sie die Welt des T Flip-Flop, eine wesentliche Komponente in der digitalen Elektronik, die für die Fähigkeit, die Zustände zu wechseln, bekannt ist.In diesem Artikel wird der Grundvorgang eingeführt und zeigt, wie sie die Ausgangszustände mit jedem Taktpuls wechseln.Wir werden die praktischen Verwendungen des T Flip-Flops, einschließlich Frequenzabteilung, Ereigniszählung und binärer Zählen, abdecken, wobei sie sich auf ihre Effizienz und das einfache Design konzentrieren.Wir werden Methoden diskutieren, um die Leistung des T Flip-Flop zu optimieren, indem wir Faktoren wie Ausbreitungsverzögerung, Stromverbrauch und Raumeffizienz behandeln.Der Prozess der Konvertierung eines T-Flip-Flops in andere Typen wie JK- und SR-Flip-Flops wird ausführlich mit praktischen Schritten und Erkenntnissen beschrieben.Dieser umfassende Leitfaden zielt darauf ab, die Vielseitigkeit und wichtige Rolle des T-Flip-Flop im modernen digitalen Schaltungsdesign zu veranschaulichen.

Katalog

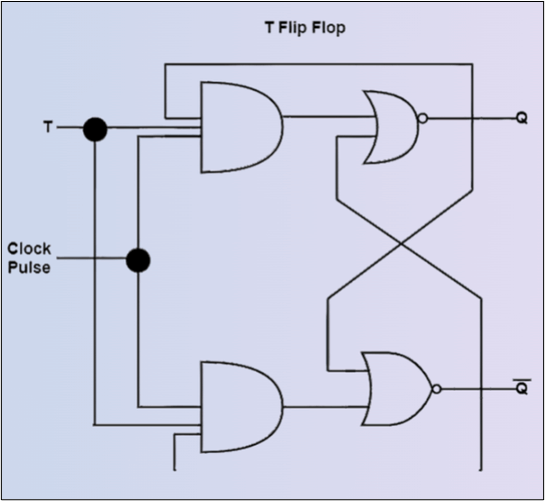

Abbildung 1: t type Flip-Flip

Erkundung von T-Flip-Flops

T Flip-Flops spielen eine wichtige Rolle bei der digitalen Elektronik für ihre Fähigkeit, die Ausgangszustände mit jedem Taktpuls zu umschalten.Diese Umschaltfunktion macht sie zu einer Schlüsselkomponente in sequentiellen Logikschaltungen.Bei der Konfiguration ändert T Flip-Flops den Zustand mit jedem Taktzyklus und bietet einen einfachen und dennoch effektiven Mechanismus zum Umschalten.Ihr Design ist unkompliziert und effizient und macht sie vielseitige Werkzeuge für digitale Schaltungsdesigner.

Zum Beispiel wechselt in einem binären Zähler-Setup den T-Flip-Flop mit jedem Taktpuls, sodass die Anzahl in Erhöhung des Zählens ermöglicht.Diese Umschaltfähigkeit ist in vielen Anwendungen von grundlegender Bedeutung und bietet eine zuverlässige Lösung für Frequenzverwaltung und sequentielle Operationen.

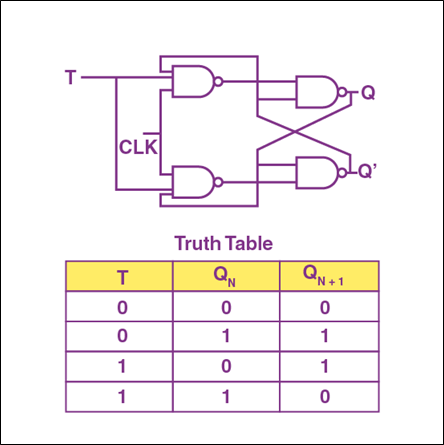

Abbildung 2: T Flip-Flop-Wahrheitstabelle und Schaltpläne

T Flip-Flops werden in verschiedenen praktischen elektronischen Systemen über theoretische Übungen hinaus verwendet.Eine signifikante Anwendung ist die Frequenzteiler.T Flip-Flops halbieren Sie die Frequenz eines Taktsignals, das für Timing- und Synchronisationsaufgaben erforderlich ist.In einer digitalen Uhr teilt beispielsweise ein T-Flip-Flop die Eingangsfrequenz, um genaue Zeitintervalle zu erzeugen.

Zusätzlich dienen T-Flip-Flops als Binärzusammen mit digitalen Uhren, Ereigniszählern und spezifischen Speichertypen.Sie sind auch in größere integrierte Schaltkreise eingebettet, um als Kippschalter zu fungieren, wodurch komplexe Logikschaltungsdesigns vereinfacht werden.Ihre Robustheit und Vorhersehbarkeit machen sie ideal für Anwendungen, die zuverlässiger Zustandsumschaltungen und Frequenzmanagement erfordern.

In Mikrocontrollern verwaltet T Flip-Flops verschiedene Zeitfunktionen, um den genauen Betrieb des Geräts zu gewährleisten.Diese realen Anwendungen zeigen die unschätzbare Rolle von T-Flip-Flops sowohl in einfachen als auch in ausgefeilten elektronischen Designs.

Um die Leistung und Zuverlässigkeit von T Flip-Flops zu optimieren, sind strategische Designverbesserungen erforderlich.Die Minimierung der Ausbreitungsverzögerung ist der Schlüssel zur Verbesserung der Geschwindigkeit des Flip-Flop.Sorgfältige Transistorgrößen und fortschrittliche Herstellungstechniken können die Verzögerungszeiten erheblich reduzieren.Beispielsweise verringert die Verwendung kleinerer Transistoren die Kapazität und führt zu schnelleren Schaltzeiten.

Stromverbrauch ist ein weiterer kritischer Faktor.Effiziente Konstruktionspraktiken wie dynamisches Leistungsmanagement und Modi mit geringer Leistung verringern den Energieausdruck von T-Flip-Flops.Techniken wie das Gating-Gating minimieren den Stromverbrauch, wenn der Flip-Flop inaktiv ist.

Raumeffizienz ist auch ein wichtiges Problem, insbesondere in dicht gepackten integrierten Schaltungen.Die moderne CMOS -Technologie ermöglicht kompaktere Layouts und spart Siliziumimmobilien.Das Integration von Fehlerprüfmechanismen sorgt außerdem sicher, dass die Zuverlässigkeit in Anträgen mit hohen Einsätzen.Beispielsweise können Paritätsprüfungen Fehler im Status des Flip-Flop erkennen, um einen zuverlässigen Betrieb zu gewährleisten.

Umwandlung eines T-Flip-Flops in JK Flip-Flop

Um das Umwandeln eines T-Flip-Flops in einen JK Flip-Flop erfordert das Verständnis der betrieblichen Prinzipien beider Typen.Ein T-Flip-Flop verfügt über einen einzelnen Umschalteingang (t), der den Status mit jedem Taktimpuls ändert, wenn T hoch ist und ihn auf den Umschalten von Vorgängen beschränkt.Im Gegensatz dazu verfügt ein JK Flip-Flop über zwei Eingänge (J und K), die mehr Kontrolle bieten.Ziel ist es, eine Schaltung zu entwerfen, die das Verhalten des JK Flip-Flop mithilfe des T Flip-Flop nachahmt.Dies beinhaltet die Emulation der Flexibilität und Kontrolle des JK Flip-Flop in der einfacheren T-Flip-Flop-Struktur.

Analyse der Wahrheitstabelle

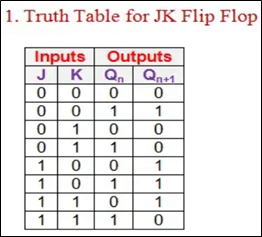

Abbildung 3: Wahrheitstabelle für JK Flip-Flop

Beginnen Sie mit der Analyse der JK Flip-Flop-Wahrheitstabelle, die zeigt, wie der nächste Status (q_ (n+1)) vom aktuellen Status (q_n) abhängt und J und K eingibt:

J = 0, K = 0: Der Zustand bleibt konstant.

J = 0, K = 1: Flip-Flop-Resets (q_ (n+1) = 0).

J = 1, K = 0: Flip-Flop-Sets (q_ (n+1) = 1).

J = 1, K = 1: Flip-Flop schaltet den Zustand um.

Das Verständnis dieser Übergänge ist wichtig, um das Verhalten des JK-Flip-Flop mit dem T Flip-Flop zu replizieren.

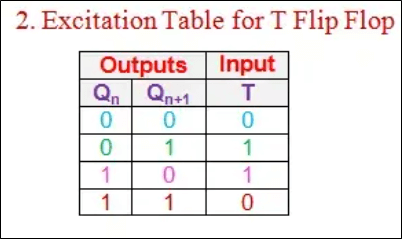

Abfertigung des Anregungstisches für T Flip-Flop

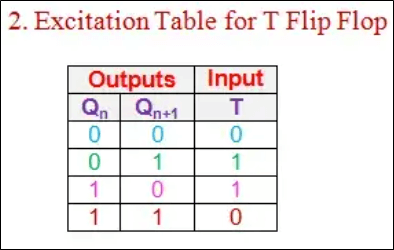

Abbildung 4: Anregungstabelle für T Flip-Flop

Leiten Sie als nächstes die T-Flip-Flop-Anregungstabelle ab und zeigen den für Zustandsübergänge benötigten T-Eingang:

Q_n = 0, q_ (n+1) = 0: t = 0.

Q_n = 0, q_ (n+1) = 1: t = 1.

Q_n = 1, q_ (n+1) = 0: t = 1.

Q_n = 1, q_ (n+1) = 1: t = 0.

In diesem Schritt wird klargestellt, wie sich die T -Eingabe für die gewünschten Zustandsübergänge basierend auf den J- und K -Eingaben verhalten sollte.

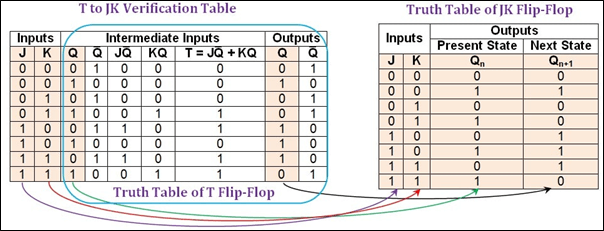

Erstellen der Conversionstabelle

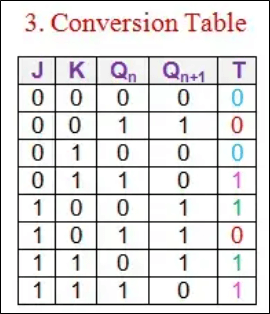

Abbildung 5: Konvertierungstabelle

Kombinieren

J, k, q_n und t:

J = 0, k = 0: t = 0 (Zustand halten).

J = 0, k = 1: t = 1 (Status zurücksetzen).

J = 1, k = 0: t = 1 (Set Status).

J = 1, k = 1: t = ¬q_n (Toggle -Status).

Diese Zuordnung leitet den booleschen Ausdruck für die Umwandlung des T-Flip-Flop in einen JK-Flip-Flop ab.

Ableiten des erforderlichen boolenen Ausdrucks

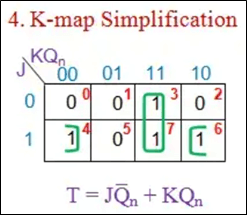

Abbildung 6: K-Map-Vereinbarung

Leiten Sie den booleschen Ausdruck für T: aus der Konvertierungstabelle ab:

T = J.®q_n + k.q_n.

Dieser Ausdruck stellt sicher, dass der T-Eingang den Status korrekt setzt, zurücksetzt oder umschaltet, wie das Verhalten des JK Flip-Flop.

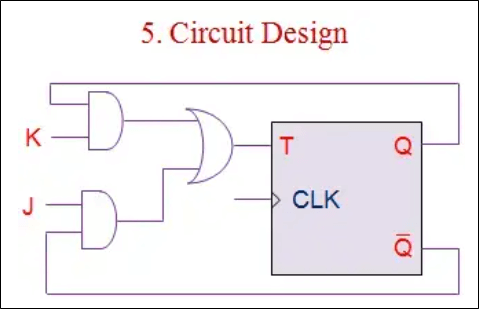

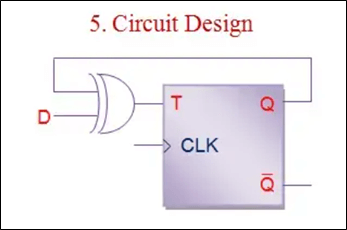

Implementierung des Schaltungsdesigns

Abbildung 7: Schaltungsdesign

Implementieren Sie die Schaltung mit grundlegenden Logik -Toren:

Verwenden und, und nicht Gates, um den booleschen Expression t = J. -q_n + k.q_n zu konstruieren.

Füttern Sie J und ¬q_n in ein und ein Tor.

Füttern Sie K und q_n in ein anderes und ein Tor.

Kombinieren Sie diese und die Gates von Gates in einem oder Gate, wobei die endgültige Ausgabe als T-Eingang für den T-Flip-Flop.

Dies stellt sicher, dass das T-Flip-Flop das Verhalten des JK Flip-Flop nachahmt.

Überprüfen des Konvertierungsprozesses

Abbildung 8: Überprüfungsprozess

Um die Konvertierung zu überprüfen:

Listen Sie alle möglichen J- und K-Eingänge und den aktuellen Status Q für den JK Flip-Flop auf.

Berechnen Sie die Zwischenwerte JQ und ¬KQ.

Verwenden Sie T = JQ + ¬KQ, um T für den T-Flip-Flop zu bestimmen.

Wenden Sie den T-Eingang auf den T-Flip-Flop an und überprüfen Sie die Ausgänge (q und q).

Vergleichen Sie diese Ausgänge mit dem erwarteten nächsten Zustand (Q ') aus der Wahrheitstabelle des JK Flip-Flop.

Dieser Prozess stellt sicher, dass die Konvertierung das Verhalten des JK Flip-Flop genau emuliert.

Umwandlung eines T-Flip-Flops in einen SR-Flip-Flop

Um das Umwandeln eines T-Flip-Flops in einen SR-Flip-Flop zu verstehen, werden die betrieblichen Prinzipien beider Flip-Flops verstanden.Ein T-Flip-Flop arbeitet mit einem einzelnen Toggle-Eingang (t), wodurch der Zustand mit jedem Taktpuls geändert wird, wenn T hoch ist, was ihn auf die Umschaltfunktionen einschränkt.Im Gegensatz dazu verfügt ein SR-Flip-Flop über zwei Eingänge, S (SET) und R (Reset), was mehr Kontrolle bietet.Ziel ist es, eine Schaltung zu entwerfen, die das Verhalten des SR Flip-Flop unter Verwendung des T Flip-Flop nachahmt.

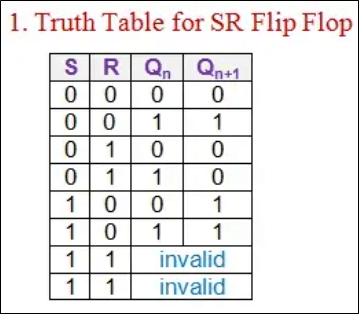

Analyse der Wahrheitstabelle

Abbildung 9: Wahrheitstabelle für SR Flip-Flop

Beginnen Sie mit der Untersuchung des SR Flip-Flop-Wahrheitstabelle:

S = 0, r = 0: Zustand bleibt konstant.

S = 0, R = 1: Flip-Flop-Resets (q_ (n+1) = 0).

S = 1, R = 0: Flip-Flop-Sets (q_ (n+1) = 1).

S = 1, r = 1: Zustand ist ungültig.

Das Verständnis dieser Zustandsübergänge ist wichtig für die Entwicklung der Logik, die zur Emulierung des SR-Flip-Flop mit dem T Flip-Flop erforderlich ist.

Abfertigung des Anregungstisches für T Flip-Flop

Abbildung 10: Anregungstabelle für T Flip-Flop

Leiten Sie als nächstes den T-Flip-Flop-Anregungstabelle ab:

Q_n = 0, q_ (n+1) = 0: t = 0.

Q_n = 0, q_ (n+1) = 1: t = 1.

Q_n = 1, q_ (n+1) = 0: t = 1.

Q_n = 1, q_ (n+1) = 1: t = 0.

Dieser Schritt verdeutlicht, wie sich die T -Eingabe verhalten sollte, um die gewünschten Zustandsübergänge basierend auf den S- und R -Eingängen zu erreichen.

Erstellen der Conversionstabelle

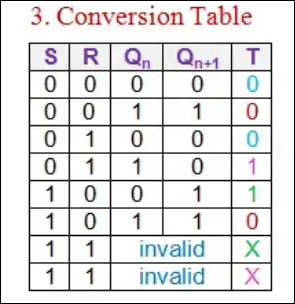

Abbildung 11: Konvertierungstabelle

Kombinieren Sie die Tabelle der SR Flip-Flop-Wahrheit mit der Tabelle T Flip-Flop, um die Konvertierungstabelle zu erstellen und die Beziehung zwischen S, R, Q_N und T zuzuordnen:

S = 0, r = 0: t = 0 (Zustand halten).

S = 0, r = 1: t = 0 (Zurücksetzen des Zustands).

S = 1, r = 0: t = 1 (Set Status).

S = 1, r = 1: Zustand ist ungültig, T ist "egal".

Diese Zuordnung leitet den booleschen Ausdruck zum Umwandeln des T-Flip-Flop in einen SR-Flip-Flop ab.

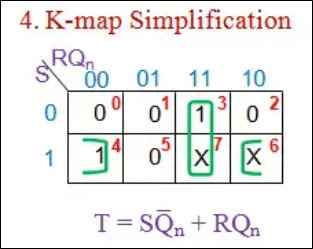

Ableiten des erforderlichen boolenen Ausdrucks

Abbildung 12: K-Map-Vereinfachung

Verwenden Sie eine Karnaugh-Karte (K-MAP) zur Vereinfachung, leiten Sie den booleschen Ausdruck für t:

T = S. + q_n + r.q_n.

Dies stellt sicher, dass T den richtigen Wert zum festgelegten, zurücksetzen oder aufrechterhaltenen Zustand gemäß dem Verhalten des SR Flip-Flop bietet.

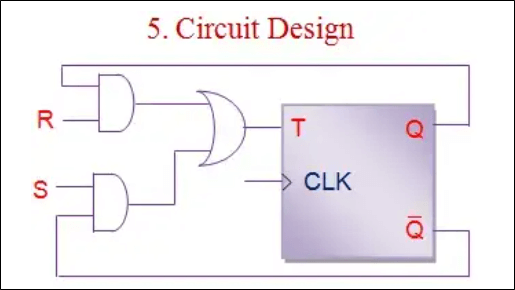

Implementierung des Schaltungsdesigns

Abbildung 13: Schaltungsdesign

Implementieren Sie die Schaltung mit grundlegenden Logik -Toren:

Verwenden Sie und, und nicht, und nicht Gates, um den booleschen Expression t = s.gr.n + r.q_n zu konstruieren.

Füttere S und ¬q_n in ein und ein Tor.

Füttern Sie R und q_n in ein anderes und ein Tor.

Kombinieren Sie diese und die Gates von Gates in einem oder Gate, wobei die endgültige Ausgabe als T-Eingang für den T-Flip-Flop.

Dies stellt sicher, dass das T-Flip-Flop das Verhalten des SR Flip-Flop nachahmt.

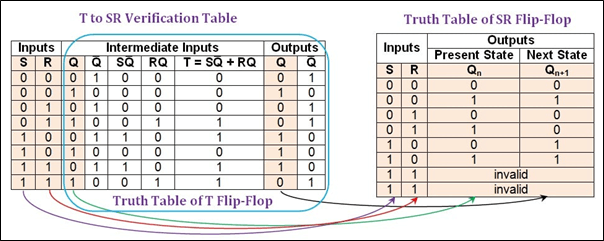

Überprüfen des Konvertierungsprozesses

Abbildung 14: Überprüfungsprozess

Um die Konvertierung zu überprüfen:

Listen Sie alle möglichen S- und R-Eingänge und den aktuellen Status Q für den SR Flip-Flop auf.

Berechnen Sie Zwischenwerte SQ und RQ.

Verwenden Sie t = S. + q_n + r.q_n, um T für den T Flip-Flop zu bestimmen.

Wenden Sie den T-Eingang auf den T-Flip-Flop an und überprüfen Sie die Ausgänge (q und q).

Vergleichen Sie diese Ausgänge mit dem erwarteten nächsten Status (q ') aus der SR

Flip-Flops Wahrheitstabelle.

Dieser Prozess stellt sicher, dass die Umwandlung das Verhalten des SR Flip Flop genau emuliert.

Umwandlung eines T-Flip-Flops in ein D Flip-Flop

Um das Umwandeln eines T-Flip-Flops in einen D Flip-Flop erfordert ein solides Verständnis der Funktionsweise beider Typen.Ein T-Flip-Flop verfügt über einen einzelnen Umschalteingang (t), der seinen Zustand mit jedem Taktimpuls ändert, wenn T hoch ist, und beschränkt ihn auf einfache Umschaltungsfunktionen.Ein D Flip-Flop hat dagegen einen einzelnen Eingang (d), bei dem der Ausgang diesen Eingang direkt bei jedem Taktpuls folgt.Ziel ist es, dass sich das T-Flip-Flop wie ein D Flip-Flop durch Entwerfen einer geeigneten Schaltung versteckt.

Analyse der Wahrheitstabelle

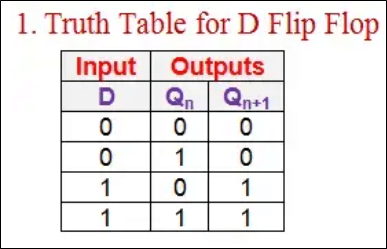

Abbildung 15: Wahrheitstabelle für D Flip-Flop

Untersuchen Sie zunächst die Tabelle der D Flip-Flop-Wahrheit:

Wenn d = 0 ist, beträgt q_ (n+1), unabhängig vom aktuellen Zustand.

Wenn d = 1 ist, ist q_ (n+1) 1, unabhängig vom aktuellen Zustand.

Das Verständnis dieser Zustandsübergänge hilft bei der Entwicklung einer Logik, die T-Flip-Flops verwendet, um D Flip-Flops zu emulieren.

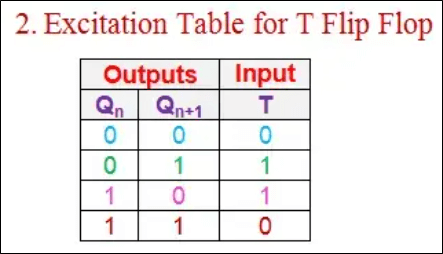

Abfertigung des Anregungstisches für T Flip-Flop

Abbildung 16: Anregungstabelle für T Flip-Flop

Leiten Sie als nächstes den T-Flip-Flop-Anregungstabelle ab:

Q_n = 0, q_ (n+1) = 0: t muss 0 sein.

Q_n = 0, q_ (n+1) = 1: t muss 1 sein.

Q_n = 1, q_ (n+1) = 0: t muss 1 sein.

Q_n = 1, q_ (n+1) = 1: t muss 0 sein.

Diese Tabelle zeigt die T -Eingabe, die erforderlich ist, um die gewünschten Zustandsübergänge basierend auf dem aktuellen Zustand und dem Eingang D zu erreichen.

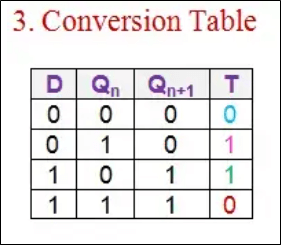

Erstellen der Conversionstabelle

Abbildung 17: Konvertierungstabelle

Kombinieren Sie die Tabelle der T-Flip-Flop-Wahrheit mit der T-Flip-Flop-Anregungstabelle, um die Konvertierungstabelle zu erstellen:

D = 0, q_n = 0: t sollte 0 sein (Status halten).

D = 0, q_n = 1: t sollte 1 sein (Umschaltungszustand).

D = 1, q_n = 0: t sollte 1 sein (Umschaltungszustand).

D = 1, q_n = 1: t sollte 0 sein (Zustand halten).

Diese Zuordnung leitet den booleschen Ausdruck für die Umwandlung des T-Flip-Flop in einen D Flip-Flop ab.

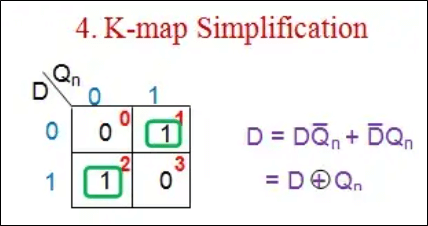

Ableiten des erforderlichen boolenen Ausdrucks

Abbildung 18: K-Map-Vereinfachung

Verwenden Sie eine Karnaugh-Karte (K-MAP) zur Vereinfachung, leiten Sie den booleschen Ausdruck für t:

T = d ⊕ q_n (wobei ⊕ die XOR -Operation bezeichnet).

Dies stellt sicher, dass T den richtigen Wert bietet, um den Zustand gemäß dem Verhalten des D Flip-Flop zu umschalten oder aufrechtzuerhalten.

Implementierung des Schaltungsdesigns

Abbildung 19: Schaltungsdesign

Um die Schaltung zu implementieren:

Verwenden Sie ein XOR -Gate, um den booleschen Expression t = d ⊕ q_n zu konstruieren.

Füttern Sie den D -Eingang und den aktuellen Status q_n in das XOR -Gate.

Die Ausgabe dieses XOR-Tors dient als T-Eingang für den T-Flip-Flop.

Dies stellt sicher, dass sich der T-Flip-Flop wie ein D Flip-Flop verhält und den erforderlichen T-Eingangsschaltet oder die Aufrechterhaltung des Status basierend auf dem D-Eingang bereitstellt.

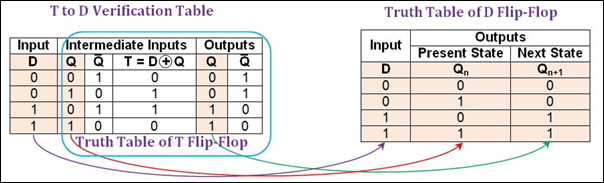

Überprüfen des Konvertierungsprozesses

Abbildung 20: Überprüfungsprozess

Um die Konvertierung zu überprüfen:

Listen Sie alle möglichen Kombinationen von Inputs (D) und den aktuellen Zustand (q) für den D Flip-Flop auf.

Berechnen Sie den Zwischenwert mit T = D ⊕ Q.

Wenden Sie den berechneten T-Eingang auf den T-Flip-Flop an.

Bestimmen Sie die resultierenden Ausgänge (q und q).

Vergleichen Sie diese Ausgänge mit dem erwarteten nächsten Status (Q ') aus der Wahrheitstabelle des D Flip-Flop.

Diese schrittweise Überprüfung stellt sicher, dass das T-Flip-Flop das Verhalten des D Flip-Flop genau emuliert.

Herausforderungen und Lösungen bei der T-Flip-Flop-Konvertierung

Das Umwandeln von T-Flip-Flops in andere Typen wie D oder JK Flip-Flops beinhaltet mehrere Herausforderungen, die sorgfältig geleitet werden müssen, um ein zuverlässiges und effektives Design zu gewährleisten.Diese Herausforderungen können sich auf die Leistung und Funktionalität des endgültigen Stromkreises auswirken, wenn sie nicht ordnungsgemäß behandelt werden.In diesem Abschnitt werden gemeinsame Probleme untersucht, die während des Konvertierungsprozesses auftreten und praktische Lösungen bereitstellen.

Eine große Herausforderung besteht darin, Zeitpunkte zu verwalten.Der genaue Zeitpunkt der Signale ist erforderlich, damit Flip-Flops korrekt funktionieren, und alle Diskrepanzen können zu falschen Zustandsübergängen führen.Timing-Probleme ergeben sich häufig aus dem Takt-Versatz, bei dem das Taktsignal zu leicht unterschiedlichen Zeiten unterschiedliche Flip-Flops erreicht und Synchronisationsprobleme verursacht.Ein weiteres häufiges Problem ist die Signalintegrität, bei der Rauschen und Signalabbau zu einem unzuverlässigen Betrieb führen können.Dies ist insbesondere in Hochfrequenzschaltungen oder Umgebungen mit signifikanten elektromagnetischen Interferenzen (EMI) problematisch.

Signalintegritätsprobleme beziehen sich auf die Qualität der Verbindungen und das Schaltungslayout.Schlechtes Layout kann das Übersprechen zwischen Signalen einführen, bei denen ein Signal versehentlich ein anderes betrifft, was zu unvorhersehbarem Verhalten führt.Lange Signalwege können Verzögerungen und Reflexionen verursachen, was eine weitere beeinträchtige Signalintegrität beeinträchtigt.Sicherstellen, dass alle Signale sauber und gut abgestimmt sind, ist der Schlüssel für einen zuverlässigen Flip-Flop-Betrieb.Diese Probleme erfordern sorgfältige Berücksichtigung und präzise Designtechniken, um ihre Auswirkungen zu mildern.

Die Bewältigung dieser Herausforderungen und die Gewährleistung erfolgreicher Conversions erfordert eine effektive Fehlerbehebung.Ein praktischer Tipp für die Verwaltung von Timing -Problemen ist die Verwendung der richtigen Taktverteilungstechniken.Gestalten Sie die Schaltung so, dass das Taktsignal alle Flip-Flops gleichzeitig erreicht und die Taktscheibe minimiert.Techniken wie die Verwendung eines dedizierten Taktverteilungsnetzwerks oder Taktpuffer können dazu beitragen, diese Synchronisation zu erreichen.Sicherstellen, dass das Taktsignal gleichmäßig verteilt ist, behält die Zeitintegrität über den Stromkreis bei.

Um Signalintegritätsprobleme zu bedenken, achten Sie auf das Layout der PCB (gedruckte Leiterplatte).Halten Sie die Signalwege kurz und direkt, um Verzögerungen zu reduzieren und den Signalabbau zu verhindern.Verwenden Sie Bodenebenen und ordnungsgemäße Abschirmung, um die Auswirkungen von EMI und Übersprechen zu minimieren.Stellen Sie außerdem sicher, dass alle Verbindungen sicher und korrosionsfrei sind, um intermittierende Fehler zu verhindern, die zu einem unzuverlässigen Betrieb führen können.Die Übernahme dieser Praktiken verbessert die Signalqualität und -zuverlässigkeit erheblich.

Ein weiterer praktischer Ansatz besteht darin, die Schaltung vor dem Erstellen zu simulieren.Simulationstools können potenzielle Probleme mit Timing und Signalintegrität identifizieren, bevor sie sich im physischen Schaltkreis manifestieren.Durch die Analyse von Simulationsergebnissen können Anpassungen vorgenommen werden, um alle identifizierten Probleme anzugehen.Diese präventive Fehlerbehebung kann Zeit und Ressourcen sparen, indem Probleme zu Beginn des Entwurfsprozesses fangen und korrigiert werden.Simulationen bieten einen virtuellen Testboden, um das Design vor der tatsächlichen Implementierung zu optimieren.

Abschluss

T-Flip-Flops sind aufgrund ihrer Umschaltfunktionen für die digitale Schaltung von wesentlicher Bedeutung und machen sie ideal für Aufgaben wie Frequenzabteilung und binäre Zählung.Sie werden in verschiedenen Anwendungen verwendet, von Frequenzteilern bis hin zu binären Zähler in digitalen Systemen.

Um T-Flip-Flops zu optimieren, muss man Probleme wie Ausbreitungsverzögerung, Stromverbrauch und Raumeffizienz behandeln.Diese Optimierungen gewährleisten ihre Wirksamkeit in der modernen Elektronik.Die Fähigkeit, T-Flip-Flops in andere Typen wie JK- oder SR-Flip-Flops umzuwandeln, unterstreicht ihre Anpassungsfähigkeit und Nützlichkeit.Durch die Beherrschung dieser Konvertierungsprozesse können Designer die Flexibilität und Kontrolle der Schaltung verbessern.T Flip-Flops ist in der digitalen Elektronik weiterhin zuverlässig und wertvoll und bietet robuste Lösungen für sequentielle Logikoperationen.

Häufig gestellte Fragen [FAQ]

1. Was ist die Hauptfunktion eines T-Flip-Flop in digitaler Elektronik?

Ein T-Flip-Flop oder ein Flip-Flop umschaltet, ändert seinen Ausgangszustand mit jedem Taktimpuls, wenn der T-Eingang hoch ist.Diese Umschaltungsfunktion ist nützlich für Aufgaben wie Frequenzabteilung, Ereigniszählung und binäre Zählung.In einer digitalen Uhr schaltet jeder Impuls den T-Flip-Flop um und hilft bei einer genauen Zeitmessung.Diese Aktion vereinfacht das sequentielle Logikschaltungsdesign und macht T-Flip-Flops aufgrund ihres einfachen und effizienten Betriebs wertvoll.

2. Wie unterscheidet sich ein T-Flip-Flop von einem JK-Flip-Flop?

Ein T-Flip-Flop ist eine einfachere Version eines JK-Flip-Flop.Ein JK Flip-Flop verfügt über zwei Eingänge, J und K, die den Ausgang je nach Kombination einstellen, zurücksetzen oder umschalten können.In einem T-Flip-Flop sind die J- und K-Eingänge miteinander verbunden.In diesem Setup wird der T-Flip-Flop den Ausgangszustand mit jedem Taktpuls umschalten, wenn der T-Eingang hoch ist.Diese Vereinfachung verringert die Komplexität des Schaltkreises, während die Umschaltfunktionalität beibehalten wird und Design und Implementierung erleichtert.

3. Umwandlung eines T-Flip-Flops in einen JK-Flip-Flop

Um einen T-Flip-Flop in einen JK-Flip-Flop umzuwandeln, untersuchen Sie zunächst die JK Flip-Flop-Wahrheitstabelle, um seine Zustandsübergänge basierend auf Eingabewerten zu erfassen.Erstellen Sie dann die Anregungstabelle von T Flip-Flop, um den für jeden Übergang benötigten T-Eingang zu identifizieren.Legen Sie als nächstes eine Konvertierungstabelle fest, in der die Korrelation zwischen J- und K -Eingängen, dem aktuellen Zustand (q) und den erforderlichen T -Eingaben beschrieben wird.Formulieren Sie aus diesen Informationen die booleschen Gleichungen, die JK -Eingänge in die entsprechende T -Eingabe umwandeln.Zusammenstellen Sie den Schaltkreis mithilfe und oder nicht von Toren, um eine JK Flip-Flop-Funktionalität mit einem T-Flip-Flop zu replizieren.Dieser strukturierte Prozess stellt sicher, dass die Umwandlung sowohl präzise als auch effektiv ist.

4. Optimierung von T Flip-Flop-Leistung

Um die Leistung von T-Flip-Flops zu verbessern, berücksichtigen Sie diese Entwurfsstrategien: Erstens minimieren Sie die Ausbreitungsverzögerung, indem Sie kleinere Transistoren und hochmoderne Herstellungstechniken einsetzen, um die Schalterzeiten zu verkürzen.Zweitens, adressieren Sie die Leistungseffizienz durch Verwendung dynamischer Leistungsmanagement und Uhr-Gating, um den Energieverbrauch zu senken, wenn der Flip-Flop im Leerlauf ist.Drittens nutzen Sie die moderne CMOS -Technologie für kompakte Schaltungslayouts und sparen Sie wertvolle Chipraum.Schließlich steigern Sie die Zuverlässigkeit durch die Integration von Fehlererkennungsfunktionen wie Paritätsprüfungen, um genaue Vorgänge in kritischen Anwendungen zu gewährleisten.Diese Taktiken verbessern gemeinsam die Geschwindigkeit, Effizienz und Zuverlässigkeit von T-Flip-Flops in elektronischen Geräten.

5. Anwendungen von T-Flip-Flops

T Flip-Flops werden in verschiedenen Anwendungen für ihre unkomplizierte und zuverlässige Leistung bevorzugt.Sie sind bei Frequenzteilern von entscheidender Bedeutung, bei denen sie die Frequenz des Taktsignals reduzieren und bei präzisem Timing und Synchronisation über die Schaltkreise hinweg helfen.Sie fungieren als binäre Zähler in Geräten wie digitalen Uhren und Ereigniszähler und bieten genaue Zählfunktionen für Ereignisse oder Zeiträume.Zusätzlich werden T-Flip-Flops als Kippschalter in integrierten Schaltungen verwendet, wodurch einfachere Designs komplexer Logikschaltungen ermöglichen, indem eine effiziente Umschaltfunktion anbietet.Ihre Haltbarkeit und ihr vorhersehbares Verhalten machen sie ideal für Rollen, die konsistente Zustandsumschaltungen und effektive Frequenzregelung in einer Reihe elektronischer Systeme erfordern.

Verwandter Blog

-

Netzteilspannung Abkürzung: VCC VDD VEE VSS GND

2024/06/6

Im modernen elektronischen Schaltungsdesign, Verständnis der Abkürzungen der Stromversorgungsspannung (wie VCC, VDD, VEE, VSS, GND).Diese Abkürzung... -

Ein Überblick über TTL- und CMOS -ICs und wie Sie zwischen ihnen wählen

2024/04/13

In diesem Artikel werfen wir einen detaillierten Blick auf zwei wichtige elektronische Technologien, komplementäre Metaloxid-Halbleiter (CMOS) und Tr... -

Verschiedene Arten von Sicherungen und Anwendungen

2024/04/18

Sicherungen sind wesentliche Komponenten in modernen elektrischen Systemen und fungieren als entscheidende Beschützer vor Überstrom.Sie arbeiten, in... -

Verständnis des C1815 -Transistors: Pinouts, Schaltungssymbole, Anwendungsschaltungen

2023/12/20

Welche Art von Röhre ist der C1815?C1815 Triode PinoutC1815 ModellzeichnungC1815 -ParameterC1815 EigenschaftenAnwendung von C1815 Der C1815 -Transist... -

LR44 -Batterien: LR44 -Batterieäquivalente und LR44 -Batterieersatz

2024/01/24

In einem sich schnell entwickelnden technologischen Gebiet, in dem die Größe der elektronischen Geräte weiter schrumpfen und dennoch alltäglicher ... -

Leitfaden zu Buck-, Boost- und Buck-Boost-Konverter

2023/12/21

Was ist ein Buck -Konverter?Wie funktioniert ein Buck Converter?Was ist ein Boost -Konverter?Wie funktioniert ein Boost -Konverter?Was ist ein Auftrie... -

Gesamtzahl der Transistoren in einer CPU

2024/06/14

In der modernen Computertechnologie ist die Beziehung zwischen der zentralen Verarbeitungseinheit (CPU) und den Transistoren zunehmend integraler gewo... -

Grundkenntnisse über Sicherungen: Merkmale, Arbeitsprinzipien, Typen und wie man richtig auswählt

2024/04/10

Sicherungen schützen Schaltungen vor Schäden aufgrund von Überlastung oder Kurzstrecken.Dieses einfache, aber geniale Gerät basiert auf einem leic... -

Wie viele Spannungen sollte eine Autokatterie haben?

2024/08/25

Ist es wirklich genug zu sagen, dass eine Batterie bei 11,9 Volt oder höher "vollständig aufgeladen" ist?Diese Zahl bietet eindeutig eine Grundlinie... -

Grunde elektronische Grundkomponenten verstehen - Widerstände, Kondensatoren, Dioden, Transistoren, Induktoren und digitale Logik -Tore

2024/04/13

Elektronische Komponenten sind der Eckpfeiler des Bauens und der Optimierung elektronischer Schaltkreise.Von gewöhnlichen Haushaltsgeräten bis hin z... -

Beherrschen analoge und digitale Schaltungen: Ein Anfängerführer

2023/12/20

Definition und Eigenschaften von analogen Schaltungen und digitalen SchaltungenDer Unterschied zwischen analogen Schaltungen und digitalen Schaltungen... -

Transistor (BJT und MOSFET) Arbeitsprinzipien

2023/12/20

Arbeitsprinzip des bipolaren Junction -Transistors (BJT)Auswahl der KomponentenwerteWie wählen Sie einen Transistor?Arbeitsprinzip von MOSFETWie scha... -

Beschreiben Sie kurz die Spezifikationen, Verpackungen, das Arbeitsprinzip, die Vorteile und die Umweltauswirkungen von Lithium-Ionen-Batterien

2024/03/20

Seit der Einführung von wiederaufladbaren Blei-Säure-Batterien im Jahr 1859 wurden sie allmählich in den Gewebe des technologischen Fortschritts ei...

Heiße Teile

- 1206YD105MAT2A

- GRM1556T1H3R3CD01D

- SS39

- LCMXO2-4000HE-6MG132C

- SI3241-D-FQR

- CCBTLV3861IPWRQ1

- IS62WV1288DBLL-45TLI

- EPM240GM100I5N

- ADM1024ARUZ-REEL7

- AD8555ARZ-REEL7

- UCC28528DW

- MK64FX512VLL12

- OPA548F/500

- TSI577-10GCLV

- RT1206BRE07750KL

- VI-J40-IW

- RT0402BRE0722RL

- 6MBI100VX-120-50

- HD64F3064BF25V

- D710E002BZDHA275R

- PCF85162T/1

- EMIF1-SMIC1RF2U7

- MAX1904EAI-T

- MST7329F-LF

- LTC1100CN8

- PMEG4002EL

- AT1380AS

- CMSH1-20M

- QS5991-5JRI

- U62H64SA35

- R2S10401SP#G00T

- NJM4558D/M

- TLC2271ACPW

- X363SAM110CBPR

- MAX149BCAP

- MAX820MESE

- APT7846ADC07

- M21121G-11P

- M37481E8FP

- WJLXT905LE

- QL4016-0PF144C

- HD6437043F33

- N32G432C8L7

- EDD51163DBH-5BLS-F

- YSS920B-SZ

- MAX9140EUKT

- LTC6995HS6-2#WTRMPBF

- 0805X106M100