Alle Kategorien

-

Integrierte schaltkreise (ICS)

Integrierte schaltkreise (ICS)

- Spezialisierte ICS(35707)

- PMIC-Spannungsregler-besonderer Zweck(1598)

- PMIC-Spannungsregler-lineare Regler(572)

- PMIC-Spannungsregler-linear + Switching(499)

- PMIC-Spannungsregler-linear(27467)

- PMIC-Spannungsregler-DC DC Switching Regulators(20868)

- PMIC-Regler-DC-DC-Switching-Controller(4728)

- PMIC-Spannungs-Referenz(2128)

- PMIC-v/f und f/v-Wandler(47)

- PMIC-Thermal Management(297)

- PMIC-Supervisor(17396)

- PMIC-RMS bis DC-Wandler(555)

- PMIC-Netzteil-Controller, Monitore(723)

- PMIC-Power over Ethernet (PoE) Controller(368)

- PMIC-Power Management-spezialisierte(2708)

- PMIC-Netzschalter, Treiber laden(1429)

- PMIC-PFC (Power Factor Correction)(320)

- PMIC oder Steuerungen, ideale Dioden(290)

- PMIC-Motor-Treiber, Regler(1166)

- PMIC-Beleuchtung, Ballast-Regler(1745)

- PMIC-LED-Treiber(11607)

- PMIC-Laser-Treiber(2349)

- PMIC-Hot-Swap-Controller(2468)

- PMIC-Gate-Treiber(5085)

- PMIC-voll, Half-Bridge-Treiber(364)

- PMIC-Energy Messung(2378)

- PMIC-Display-Treiber(4466)

- PMIC-derzeitige Regulierung/Management(732)

- PMIC-Batterie-Management(3519)

- PMIC-Ladegeräte(46080)

- PMIC-AC DC Konverter, Offline Schalter(21202)

- Memory-Controller(9982)

- Memory-Konfigurations-Proms für FPGAs(7695)

- Speicher-Akkus(130)

- Memory(19527)

- Memory(19527)

- Logic-universelle Bus-Funktionen(31014)

- Logic-Übersetzer, Level-Shifter(755)

- Logik-Specialty Logic(1916)

- Logik-Signal-Schalter, Multiplexer, Decoder(3447)

- Logic-Shift-Register(6058)

- Logic-Parity Generatoren und Checkers(6682)

- Logic-multivibratoren(1274)

- Logik-Latches(1535)

- Logik - Tore und Wechselrichter - Multifunktion, konfigurierbar(4223)

- Logik-Tore und Wechselrichter(5667)

- Logic-Flip Flops(7964)

- Logik-FIFOs Speicher(1236)

- Logik-Zähler, Trennlinien(3350)

- Logik-Vergleichsoperator(5892)

- Logik-Puffer, Treiber, Receiver, Transceiver(6630)

- Linear-Video-Verarbeitung(1075)

- Linear-Vergleichsoperator(2312)

- Linear-analoge Multiplikatoren, Trennwände(1237)

- Linear-Verstärker-Video Amps und Module(3822)

- Linear-Verstärker-Spezial-Zweck(3334)

- Linear - Verstärker - Instrumentierung, OP -Verstärker, Pufferverstärker(11463)

- Linear-Verstärker-Audio(971)

- Interface-Voice Record und Playback(634)

- Schnittstelle - UARTs (Universal Asynchronous Receivers -Sender)(133)

- Schnittstelle-Telecom(47636)

- Interface-spezialisierte(1301)

- Interface-Signal Terminatoren(2351)

- Interface-Signal-Puffer, Repeater, Splitter(1834)

- Interface-Serializer, Deserializer(7226)

- Schnittstellen-Sensor und Detektor-Interfaces(2321)

- Interface-Module(230)

- Interface-Modems-ICS und Module(668)

- Interface-e/a-Expander(2822)

- Interface-Filter-aktiv(1524)

- Interface-Encoder, Decoder, Konverter(11802)

- Interface-Treiber, Receiver, Transceiver(10390)

- Interface-Direct Digital Synthesis (DDS)(3471)

- Interface-Controller(3245)

- Interface-Codecs(583)

- Schnittstelle - Analoge Switches, Multiplexer, Demultiplexer(15690)

- Schnittstelle-analoge Schalter-spezieller Zweck(2961)

- Embedded-System on Chip (SoC)(6429)

- Embedded-PLDs (programmierbare Logik-Vorrichtung)(613)

- Embedded-Mikroprozessoren(5164)

- Embedded-Mikrocontroller-anwendungsspezifische(2091)

- Embedded-Mikrocontroller(59305)

- Eingebettet - Mikrocontroller, Mikroprozessor, FPGA -Module(4518)

- Eingebettet - FPGAs (Feldprogrammiergate -Array) mit Mikrocontrollern(557)

- Embedded-FPGAs (Field Programmable Gate Array)(7189)

- Embedded-DSP (Digital Signal Processors)(4650)

- Eingebettet - CPLDs (komplexe programmierbare Logikgeräte)(4971)

- Datenerfassung-Touch Screen Controller(596)

- Datenerfassung-Digital to Analog Converter (DAC)(5044)

- Datenerfassung-digitale Potentiometer(1879)

- Datenerfassung-analog zu Digital Converters (ADC)(5134)

- Datenerfassung-analoges Frontend (AFE)(227)

- Datenerfassung-MDE/DACs-spezieller Zweck(922)

- Clock/Timing-Uhren in Echtzeit(1372)

- Uhr/Timing - programmierbare Timer und Oszillatoren(1504)

- Clock/Timing-IC-Akkus(492)

- Takt/Timing-Delay Lines(16538)

- Uhr/Timing - Uhrengeneratoren, PLLS, Frequenzsynthesizer(20093)

- Clock/Timing-Clock Puffer, Treiber(3531)

- Clock/Timing-anwendungsspezifische(3433)

- Audio Spezial-Zweck(9718)

-

Diskrete Halbleiter-Produkte

Diskrete Halbleiter-Produkte

- Aktuelle Regulierung - Dioden, Transistoren(775)

- Transistoren-besonderer Zweck(64)

- Transistoren-programmierbare Unijunction(1584)

- Transistoren-jfets(1690)

- Transistoren-IGBTs-Einzel(6032)

- Transistoren-IGBTs-Module(1087)

- Transistoren-IGBTs-Arrays(9)

- Transistoren-FETs, MOSFETs-Einzel(16037)

- Transistoren-FETs, MOSFETs-RF(3251)

- Transistoren-FETs, MOSFETs-Arrays(6376)

- Transistoren-Bipolar (BJT)-einzeln, Pre-biased(4478)

- Transistoren-Bipolar (BJT)-Einzel(12624)

- Transistoren-Bipolar (BJT)-RF(488)

- Transistoren-bipolare (BJT)-Arrays, Pre-biased(6311)

- Transistoren-bipolare (BJT)-Arrays(1394)

- Thyristor-triacs(1128)

- Thyristoren-SCRs-Module(1141)

- Thyristoren-SCRs(2752)

- Thyristoren-diacs, sidacs(164)

- Power Driver Module(4744)

- Dioden-zenerdioden-Einzel(43480)

- Dioden-zenerdioden-Arrays(113195)

- Dioden - variable Kapazität (Varik, Varaktoren)(718)

- Dioden-RF(1765)

- Dioden-Gleichrichter-Einzel(31894)

- Dioden-Gleichrichter-Arrays(8627)

- Dioden-Brücke-Gleichrichter(20238)

-

RF/if und RFID

RF/if und RFID

- SIM -Karten für Abonnenten -Identifikationsmodul (SIM)(41)

- RF -Zirkulatoren und Isolatoren(1721)

- RFID Zubehör(350)

- HF-Zubehör(2025)

- RFID, RF-Zugang, Monitoring-ICS(4567)

- RFID Transponder, Tags(240)

- RFID Lesegeräte(1877)

- RFID Evaluation und Development Kits, Boards(67)

- RFID Evaluation und Development Kits, Boards(67)

- RFID Antennen(696)

- RFI und EMI - Abschirm- und Absorbungsmaterialien(8538)

- HF und EMI-Kontakte, Fingerstock und Dichtungen(4004)

- RF Transmitter(1179)

- RF Transceiver Module(4056)

- RF-Transceiver ICS(1553)

- HF-Schalter(8107)

- RF Shields(4991)

- HF-Receiver(639)

- HF -Empfänger, Sender und Transceiver -Einheiten(3515)

- RF Power Divider/Splitter(4268)

- RF Power Controller ICs(595)

- HF-Modulatoren(3958)

- HF-Mixer(4622)

- RF misc ICS und Module(2738)

- HF-Front-End (LNA + PA)(11681)

- HF Evaluation und Development Kits, Boards(1994)

- HF Evaluation und Development Kits, Boards(1994)

- HF-gerichtete Kupplung(2963)

- RF Diplexer(1406)

- RF-Detektoren(175)

- RF-Demodulatoren(256)

- HF-Antennen(7488)

- HF-Verstärker(17487)

- Balun(706)

- Dämpfungsglieder(3204)

-

Optoelektronik

Optoelektronik

- Optomechanisch(338)

- Leuchten(125)

- Laserdioden, Lasermodule - Laserlieferung, Laserfasern(325)

- Hene Lasersysteme(24)

- Hene Lasersystemzubehör(9)

- Hene Laserköpfe(16)

- Hintergrundbeleuchtung anzeigen(31)

- Laserdioden, Module - Zubehör(36)

- Zubehör(42476)

- Zubehör(42476)

- Xenon-Beleuchtung(549)

- Touchscreen-Overlays(249048)

- Panel Indicators, Pilot Lights(47475)

- Optik-Remote-Phosphor-Lichtquelle(2771)

- Optik-Reflektoren(145)

- Optik-leichte Rohre(3353)

- Optik-Objektive(15458)

- LEDs-Spacer, Unentschieden(433)

- LEDs-Lamp-Ersetzungen(24316)

- LEDs - Leiterplattenindikatoren, Arrays, Lichtstäbe, Balkendiagramme(1922)

- LED-thermische Produkte(6703)

- LED-Beleuchtung(39)

- LED-Beleuchtung-weiß(13461)

- LED-Beleuchtung-Farbe(2210)

- LED-Beleuchtung-Maiskolben, Motoren, Module(9508)

- LED-Anzeige-diskret(10227)

- Laserdioden, Module(1345)

- Lampen-Glühlampen, Neons(338506)

- Lampen-Kälte-Fluoreszenz (KKL) & UV(349)

- Wechselrichter(7962)

- Infrarot, UV, sichtbare Strahler(3759)

- Fiber Optics-Transmitter-Antrieb integriert(3523)

- Fiber Optics-Transmitter-diskrete(2743)

- Fiber Optics-Transceiver Module(22925)

- Fiberoptik-Switches, Multiplexer, Demultiplexer(8234)

- Fiberoptik-Receiver(853)

- Fiberoptik-Dämpfung(394)

- Elektrolumineszenz(24758)

- Display, Monitor-Interface Controller(2642)

- Display-Module-Vakuum-Leuchtstofflampen (VFD)(19327)

- Module anzeigen-LED Dot Matrix und Cluster(17654)

- Display-Module-LED-Zeichen und numerische(2162)

- Display-Module-LCD, OLED, Graphic(3487)

- Display-Module-LCD, OLED-Zeichen und numerische(790)

- Display-Blenden, Objektive(288)

- Adresse, Spezialität(2442)

-

Sensoren, Wandler

Sensoren, Wandler

- Ultraschallempfänger, Sender - Industrial(115)

- Temperatursensoren - Thermostate - Mechanisch - Industrielles(1270)

- Temperatursensoren - Analog und digitaler Ausgang - Industrial(169)

- Näherungssensoren - Industrial(7143)

- Drucksensoren, Wandler - Industrie(1835)

- Optische Sensoren - Photonik - Zähler, Detektoren, SPCM (Einzelphotonzählmodul)(726)

- Optische Sensoren - Kameramodule(776)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module) - Industrie(138)

- Kraftsensoren - Industrial(265)

- Flusssensoren - Industrielles(137)

- Float, Level Sensoren - Industrial(172)

- Encoder - Industrial(2217)

- Farbsensoren - Industrial(20)

- Berührungssensoren(63)

- Messkabel-Zubehör(2553)

- Zubehör(4528)

- Zubehör(4528)

- Ultraschall-Receiver, Transmitter(986)

- Temperatursensoren-Thermostat-Solid State(333)

- Temperatursensoren-Thermostate-mechanisch(4379)

- Temperatursensoren - Thermoelemente, Temperatursonden(1770)

- Temperatursensoren - RTD (Widerstandstemperaturdetektor)(1653)

- Temperatursensoren-PTC-Thermistoren(2026)

- Temperatursensoren-ntc-thermistoren(7932)

- Temperatursensoren-Analog und Digital Output(2963)

- DMS(1886)

- Spezialisierte Sensoren(3142)

- Solarzellen(688)

- Schock-Sensoren(317)

- Sensor-Interface-Junction-Blöcke(2156)

- Sensor-Kabel-Baugruppen(26522)

- Proximity/Belegung Sensoren-fertige Einheiten(902)

- Näherungsschalter(3322)

- Drucksensoren, Wandler(10275)

- Positionssensoren - Winkel, lineare Positionsmessung(3882)

- Optische Sensoren-reflektierende-Logik-Ausgang(1471)

- Optische Sensoren - reflektierend - analoge Ausgang(1258)

- Optische Sensoren-Phototransistoren(1032)

- Optische Sensoren - Photointerrupter - Schlitztyp - Transistorausgang(513)

- Optische Sensoren - Photointerrupter - Schlitztyp - Logikausgabe(559)

- Optische Sensoren-Lichtschranke, Industrial(12132)

- Optische Sensoren-Photodioden(3168)

- Optische Sensoren-Foto-Detektoren-Remote Receiver(1350)

- Optische Sensoren-Foto-Detektoren-Logik-Ausgang(339)

- Optische Sensoren-Foto-Detektoren-CDs-Zellen(717)

- Optische Sensoren-Maus(1297)

- Optische Sensoren-Distanz-Messung(1412)

- Optische Sensoren-Ambient Light, IR, UV Sensoren(10243)

- Multifunktions(1418)

- Motion Sensors-Vibration(1680)

- Motion Sensors-Tilt Schalter(159)

- Bewegungsmelder-optisch(347)

- Motion Sensors-Neigungssensoren(102)

- Motion Sensors-Imus (Trägheit-Maßeinheiten)(298)

- Motion Sensors-Kreisel(702)

- Motion Sensors-Beschleunigungsmesser(764)

- Magnete-Sensor abgestimmt(152)

- Magnete-Multi Purpose(1871)

- Magnetische Sensoren-Schalter (Solid State)(1519)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module)(2148)

- Magnetische Sensoren-linear, Kompass (ICS)(698)

- Magnetsensoren - Kompass, Magnetfeld (Module)(178)

- LVDT -Wandler (linearer variabler Differentialtransformator)(1451)

- IrDA Transceiver-Module(77)

- Bildsensor, Kamera(1272)

- Feuchtigkeit-Sensoren(3880)

- Gas-Sensoren(4294)

- Force Sensoren(1023)

- Durchfluss-Sensoren(440)

- Float, Level Sensoren(634)

- Flex-Sensoren(157)

- Encoder(3440)

- Staub-Sensoren(388)

- Aktuelle Wandler(2256)

- Color Sensoren(49)

- Schnittstelle - Sensor, kapazitive Berührung(356)

- Verstärker(2000)

- Verstärker(2000)

-

Anschlüsse, Verbindungen

Anschlüsse, Verbindungen

- Stecker und Behälter(1710)

- USB, DVI, HDMI Stecker-Zubehör(94)

- Klemmen-Zubehör(113)

- Anschlussblöcke-Zubehör-Draht-Beschläge(1061)

- Anschlussblöcke-Zubehör-Marker-Streifen(4696)

- Anschlussblöcke-Zubehör-Jumper(1477)

- Anschlussblöcke-Zubehör(3886)

- Solid State Lighting Steckverbinder-Zubehör(96)

- Buchsen für ICS, Transistoren-Zubehör(71)

- Rechteckige Steckverbinder-Zubehör(2950)

- Rechteckig-Platine-Stecker-Zubehör(1)

- Power Entry Steckverbinder-Zubehör(329)

- Austauschbare Steckverbinder-Zubehör(204)

- Photovoltaik (Solarpanel) Stecker - Zubehör(99)

- Modulare Anschlüsse - Kabelblöcke - Zubehör(22)

- Modulare Steckverbinder-Zubehör(276)

- Memory Steckverbinder-Zubehör(57)

- Keystone-Zubehör(357)

- Heavy Duty Steckverbinder-Zubehör(1081)

- LWL-Steckverbinder - Zubehör(349)

- FFC, FPC (flache flexible) Steckverbinder - Zubehör(8)

- D -Sub, D -förmige Steckverbinder - Zubehör - JackScrews(830)

- D-Sub, d-förmige Steckverbinder-Zubehör(1168)

- Koaxial Verbinder (RF)-Zubehör(1017)

- Rundsteckverbinder-Zubehör(48982)

- Card Edge Steckverbinder-Zubehör(99)

- Blade Type Power Connectors-Zubehör(670)

- Fass-Zubehör(74)

- Banana and Tip Steckverbinder-Zubehör(25)

- Backplane Steckverbinder-Zubehör(693)

- USB, DVI, HDMI Stecker-Adapter(45761)

- USB, DVI, HDMI Stecker(3377)

- USB, DVI, HDMI Stecker(3377)

- Klemmen-Wire to Board Steckverbinder(1604)

- Klemmen-Draht-Steckverbinder(40747)

- Klemmen-Draht-Pin Stecker(12531)

- Terminals-Revolver Steckverbinder(5553)

- Terminals-spezialisierte Steckverbinder(1300)

- Klemmen-Spaten Verbinder(1381)

- Klemmen-Löten/Stecker(2577)

- Klemmen-Verschraubungen(1980)

- Klemmen-Ring Steckverbinder(6682)

- Klemmen-rechteckige Steckverbinder(3878)

- Terminals - Schnellverbindungen, schnelle Trennungsanschlüsse(4695)

- Klemmen-PC PIN, Single Post Connectors(2149)

- Klemmen-PC-Pin-Buchsen, Sockel-Steckverbinder(2222)

- Klemmen-magnetische Draht-Steckverbinder(3357)

- Klemmen-Messer Steckverbinder(3829)

- Klemmen-Gehäuse, Stiefel(1891)

- Klemmen-Folie Steckverbinder(662)

- Klemmen-Barrel, Bullet-Steckverbinder(5430)

- Klemmen-Adapter(713)

- Terminal-Streifen und Revolver-Boards(11368)

- Terminal Junction Systeme(3288)

- Anschlussblöcke-Draht an Bord(19352)

- Terminal Blocks-spezialisierte(2960)

- Terminal Blocks-Power Distribution(499)

- Anschlussblöcke-Panel Mount(522)

- Terminal Blocks-Interface Module(1639)

- Anschlussblöcke-Kopfzeilen, Stecker und Buchsen(148192)

- Anschlussblöcke-DIN-Schiene, Kanal(10920)

- Anschlussblöcke-Kontakte(306247)

- Anschlussblöcke-Barrier Blocks(44736)

- Anschlussblöcke-Adapter(449)

- Solid State Lighting Verbinder-Kontakte(2509)

- Solid State Lighting Steckverbinder(2295)

- Solid State Lighting Steckverbinder(2295)

- Buchsen für ICS, Transistoren-Adapter(765)

- Buchsen für ICS, Transistoren(2223)

- Buchsen für ICS, Transistoren(2223)

- Shunts, Jumper(821)

- Rechteckige Verbinder-Feder geladen(8043)

- Rechteckige Steckverbinder-Gehäuse(28877)

- Rechteckige Verbinder-Kopfzeilen, Spezial-PIN(5397)

- Rechteckige Anschlüsse - Header, Gefäße, weibliche Sockel(23450)

- Rechteckige Verbinder-Kopfzeilen, männliche Pins(138439)

- Rechteckige Anschlüsse - kostenloses Hängen, Panelhalterung(15074)

- Rechteckige Verbinder-Kontakte(5477)

- Rechteckige Anschlüsse - Board in, Direktdraht zum Board(2459)

- Rechteckige Verbinder-Adapter(251)

- Rechteckig - Brett zu Board -Steckern - Header, Behälter, weibliche Sockel(2982)

- Rechteckig - Brett zu Board -Steckern - Header, männliche Stifte(239)

- Rechteckige Anschlüsse - Board -Abstandshalter, Stacker (Board zu Board)(27782)

- Rechteckige Anschlüsse - Arrays, Kantentyp, Mezzanin (Board zu Board)(14186)

- Stromanschluss-Eingänge, Steckdosen, Module(4831)

- Austauschbare Steckverbinder(5229)

- Austauschbare Steckverbinder(5229)

- Photovoltaik- (Solarpanel) Anschlüsse - Kontakte(69363)

- Photovoltaik (Solar Panel) Steckverbinder(365)

- Photovoltaik (Solar Panel) Steckverbinder(365)

- Modulare Steckverbinder-Verdrahtung Blöcke(653)

- Modulare Steckverbinder-Stecker(2164)

- Modulare Steckverbinder-Stecker Gehäuse(3582)

- Modulare Steckverbinder-Buchsen mit magnetischen(4193)

- Modulare Steckverbinder-Buchsen(15464)

- Modulare Steckverbinder-Adapter(503)

- Memory Connectors-PC Cards-Adapter(859)

- Memory Connectors-PC Card Sockets(1904)

- Memory Connectors-Inline Modul Sockets(2493)

- LGH Steckverbinder(1057)

- Keystone-Einsätze(8467)

- Keystone-Frontplatte, Frames(19410)

- Heavy Duty Steckverbinder-Einsätze, Module(213354)

- Schwerlastanschlüsse - Gehäuse, Kapuzen, Basen(449460)

- Heavy Duty Steckverbinder-Frames(16851)

- Heavy Duty Steckverbinder-Kontakte(6325)

- Heavy Duty Steckverbinder-Baugruppen(1730)

- LWL-Steckverbinder-Gehäuse(4852)

- Glasfaser-Steckverbinder - Adapter(2754)

- LWL-Steckverbinder(215502)

- FFC, FPC (flache flexible) Steckverbinder - Gehäuse(30189)

- FFC, FPC (flache flexible) Anschlüsse - Kontakte(114)

- FFC, FPC (flache flexible) Steckverbinder(12920)

- FFC, FPC (flache flexible) Steckverbinder(12920)

- D-Sub, d-förmige Steckverbinder-Terminatoren(640)

- D-Sub, d-förmige Steckverbinder-Gehäuse(12383)

- D-Sub, d-förmige Steckverbinder-Kontakte(1350)

- D-Sub, D-förmige Steckverbinder-Rückenschalen, Kapuzen(3078)

- D-Sub, d-förmige Steckverbinder-Adapter(976)

- D-Sub Steckverbinder(106471)

- D-förmige Steckverbinder-Centronics(6037)

- Kontakte, Frühling geladen und Druck(7921)

- Kontakte-Multi Purpose(16222)

- Kontakte-"Leadframe"(572)

- Koaxial-Steckverbinder (RF)-Terminatoren(1374)

- Koaxial-Steckverbinder (RF)-Kontakte(279)

- Koaxial-Steckverbinder (RF)-Adapter(5909)

- Koaxial-Steckverbinder (RF)(16068)

- Koaxial-Steckverbinder (RF)(16068)

- Rundsteckverbinder-Gehäuse(221760)

- Rundsteckverbinder-Kontakte(3377)

- Rundsteckverbinder-backschalen und Kabel-Klemmen(44820)

- Rundsteckverbinder-Adapter(7708)

- Rundsteckverbinder(771637)

- Rundsteckverbinder(771637)

- Card Edge Steckverbinder-Gehäuse(577)

- Karte Edge Verbinder-edgeboard Verbinder(497865)

- Card Edge Verbinder-Kontakte(527)

- Card Edge Verbinder-Adapter(2752)

- Blade Type Power Steckverbinder-Gehäuse(2290)

- Blade Type Power Connectors-Kontakte(715)

- Blade-Typ-Stecker(2373)

- Blade-Typ-Stecker(2373)

- Zwischen Serien-Adapter(289)

- Barrel-Stromanschluss(399)

- Barrel-Audio-Anschlüsse(10808)

- Barrel-Audio Adapter(54)

- Banana und Tip Steckverbinder-Buchsen, Stecker(2046)

- Banana and Tip Connectors-Binding Posts(3219)

- Banana und Tip Steckverbinder-Adapter(647)

- Backplane Steckverbinder-spezialisiert(33926)

- Backplane Steckverbinder-Gehäuse(47465)

- Backplane Steckverbinder-Hard metrisch, Standard(7596)

- Backplane Steckverbinder-DIN 41612(4684)

- Backplane Steckverbinder-Kontakte(4419)

- Backplane Connectors-ARINC Einsätze(2322)

- Backplane Steckverbinder-ARINC(3305)

-

Widerstände

-

Kondensatoren

Kondensatoren

- Zubehör(50)

- Zubehör(50)

- Trimmer, Variable Kondensatoren(1088)

- Dünne Folien-Kondensatoren(1724)

- Tantal-Kondensatoren(79518)

- Tantal-Polymer-Kondensatoren(2486)

- Silizium-Kondensatoren(225)

- Niob Oxide Kondensatoren(128)

- Mica und PTFE Kondensatoren(908)

- Folien-Kondensatoren(89898)

- Elektrische Doppelschichtkondensatoren (EDLC), Superkondensatoren(1644)

- Keramische Kondensatoren(261123)

- Kondensatoren-Netzwerke, Arrays(740)

- Aluminium-Elektrolytkondensatoren(39501)

- Aluminium-Polymer-Kondensatoren(2396)

-

Transformatoren

Transformatoren

-

Isolatoren

-

Kristalle, Oszillatoren, Resonatoren

-

Switches

Switches

- Verriegelungsschalter(862)

- Emergency-Stop-Schalter (E-Stop)(752)

- Kabelzugschalter(353)

- Accessoires-Caps(1768)

- Zubehör-Stiefel, Dichtungen(106)

- Zubehör(11056)

- Zubehör(11056)

- Toggle-Schalter(18713)

- Rändelrads Schalter(1050)

- Schalter(9157)

- Snap-Aktion, Endschalter begrenzen(14916)

- Slide-Schalter(24680)

- Selector-Schalter(4460)

- Rotary Switches(5818)

- Rocker Schalter(60676)

- Drucktaste-Schalter-Hall-Effekt(3768)

- Drucktaste Schalter(29541)

- Programmierbare Display-Switches(13202)

- Navigations-Schalter, Joystick(14105)

- Magnetische, Reed-Schalter(604)

- Keypad-Schalter(168067)

- Keylock Schalter(1623)

- DIP Schalter(2977)

- Konfigurierbare Switch-Komponenten-Objektiv(1755)

- Konfigurierbare Schalter-Komponenten-Lichtquelle(1239)

- Konfigurierbare Switch-Komponenten-Contact Block(2781)

- Konfigurierbare Switch-Komponenten-Body(17732)

-

Relais

Relais

- Sicherheitsrelais(722)

- Reedrelais(484)

- Hochfrequenz (RF) -Relais(461)

- Schütze (Festkörper)(64)

- Schütze (elektromechanisch)(10945)

- Kfz-Relais(1280)

- Zubehör(2791)

- Zubehör(2791)

- Solid State Relais(3585)

- Signal-Relais, bis zu 2 Ampere(6811)

- Relay-Sockets(869)

- Power Relays, über 2 Ampere(369115)

- E / A-Relaismodule(593)

- I/o-Relay-Module-Input(30134)

- I/o-Relay-Module-Analog(438223)

- I/o-Relay-Modul-Racks(14318)

Sprache auswählen

Aktuelle Sprache

Deutsch

- English

- Deutsch

- Italia

- Français

- 日本語

- 한국의

- русский

- Svenska

- Nederland

- español

- Português

- polski

- Suomi

- Gaeilge

- Slovenská

- Slovenija

- Čeština

- Melayu

- Magyarország

- Hrvatska

- Dansk

- românesc

- Indonesia

- Ελλάδα

- Български език

- Afrikaans

- IsiXhosa

- isiZulu

- lietuvių

- Maori

- Kongeriket

- Монголулс

- O'zbek

- Tiếng Việt

- हिंदी

- اردو

- Kurdî

- Català

- Bosna

- Euskera

- العربية

- فارسی

- Corsa

- Chicheŵa

- עִבְרִית

- Latviešu

- Hausa

- Беларусь

- አማርኛ

- Republika e Shqipërisë

- Eesti Vabariik

- íslenska

- မြန်မာ

- Македонски

- Lëtzebuergesch

- საქართველო

- Cambodia

- Pilipino

- Azərbaycan

- ພາສາລາວ

- বাংলা ভাষার

- پښتو

- malaɡasʲ

- Кыргыз тили

- Ayiti

- Қазақша

- Samoa

- සිංහල

- ภาษาไทย

- Україна

- Kiswahili

- Cрпски

- Galego

- नेपाली

- Sesotho

- Тоҷикӣ

- Türk dili

- ગુજરાતી

- ಕನ್ನಡkannaḍa

- मराठी

CMOS -Technologie: Gestaltung des zeitgenössischen digitalen Logikdesigns

Zeit: 2024/06/20

Durchsuchen: 674

In diesem Artikel wird untersucht, wie wichtig die CMOS -Technologie für die Schaffung grundlegender Logik -Gates wie Wechselrichter, NAND, NOR und, OR und XOR -Gates ist.Entdecken Sie den detaillierten Prozess des CMOS -Schaltungsdesigns, bei dem eine sorgfältige Anordnung von Transistoren zur Miniaturisierung elektronischer Komponenten, Verbesserung der Prozessoren und des Speichers führt.

Katalog

Abbildung 1: CMOS -Technologie

Die Rolle der CMOS -Technologie im digitalen Logikdesign

Die CMOS-Technologie (Complementary Metal-Oxid-Semiconductor) spielt eine Schlüsselrolle für das moderne digitale Logikdesign, wobei die kombinierten Eigenschaften von NMOs (MOSFET) und PMOS-Transistoren (P-Typ) (P-Typ) verwendet werden.Diese Kombination ermöglicht eine hohe Leistung mit geringem Stromverbrauch, eine Notwendigkeit für die heutigen digitalen Geräte.

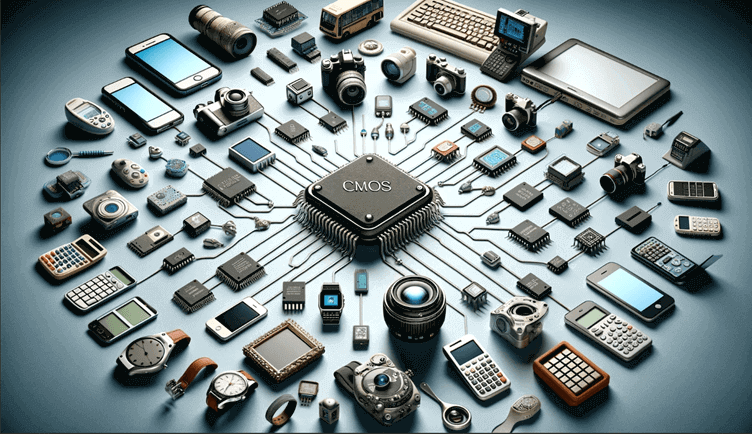

Abbildung 2: CMOS -Schaltkreis mit PMOS und NMOs konstruiert

In CMOS -Schaltkreisen arbeiten NMOS- und PMOS -Transistoren komplementär, wobei ein Transistor eingeschaltet wird, wenn der andere ausschaltet.Diese komplementäre Schaltung reduziert den Widerstand, minimiert den Stromverbrauch und sorgt für einen effizienten Stromfluss.Der Begriff "komplementär" in CMOs bezieht sich auf diesen ausgewogenen und effizienten Betrieb, was ihn ideal macht, um effektive Logik -Tore und digitale Schaltkreise zu erstellen.

Das Entwerfen von CMOS -Logik -Toren beinhaltet sorgfältige Details.Ingenieure müssen NMO- und PMOS -Transistoren sorgfältig positionieren, um die Leistung zu optimieren.Beispielsweise ist in einem Wechselrichtertor eine präzise Kontrolle der Transistorzustände erforderlich.Diese Steuerung ermöglicht die Integration von Transistoren mit hoher Dichte in einen Chip, was zur Miniaturisierung elektronischer Geräte und zur Entwicklung fortschrittlicher Prozessoren und Speichergeräte führt.

CMOS -Schaltungen sind bekannt für ihre Robustheit und Zuverlässigkeit.Sie arbeiten effizient bei niedrigeren Spannungen, wodurch der Stromverbrauch und die Wärmeerzeugung verringert werden.Dies macht sie für Hochgeschwindigkeits- und hochpräzise Anwendungen geeignet, bei denen die Integrität der Signalintegrität erforderlich ist.

Rolle von CMOS -Wechselrichtern im digitalen Logikdesign

Der CMOS -Wechselrichter ist eine grundlegende Komponente in der digitalen Logikdesign und ist sehr wichtig für den Aufbau komplexer elektronischer Schaltkreise.Der Wechselrichter besteht aus NMOs (N-Typ-Metalloxid-Halbleiter) und PMOS-Transistoren vom Metalloxid-Halbleiter-Typ-Typ (P-Typ-Metalloxid).Der NMOS -Transistor ist mit dem Boden verbunden, während der PMOS -Transistor mit der Stromversorgung verbunden ist.

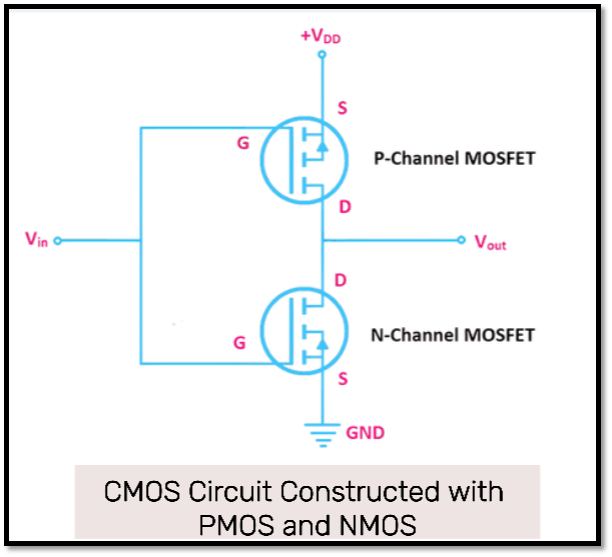

Abbildung 3: CMOS -Wechselrichterschema -Diagramm und Wahrheitstabelle

Wenn eine Hochspannung auf den Eingang angewendet wird, aktiviert der NMOS -Transistor und erzeugt einen direkten Weg zum Boden, was zu einer niedrigen Ausgangsspannung führt.Umgekehrt aktiviert eine niedrige Eingangsspannung den PMOS -Transistor und deaktiviert den NMOS -Transistor, wodurch der Ausgang mit der Stromversorgung verbunden und eine hohe Ausgangsspannung erzeugt wird.

Die Effizienz des CMOS -Wechselrichters beruht auf dem komplementären Schaltverhalten, um sicherzustellen, dass nur ein Transistor jeweils durchgeführt wird.Dieses Design minimiert den Stromverbrauch, da der Strom hauptsächlich während des Schaltvorgangs und nicht im stationären Zustand fließt.Diese Verringerung der statischen Leistungsabteilung macht CMOS -Wechselrichter für verschiedene digitale Schaltkreise, einschließlich integrierter Schaltungen (ICs) und Mikroprozessoren, geeignet.Der ausgewogene Betrieb von NMOS- und PMOS -Transistoren verbessert die Zuverlässigkeit des Wechselrichters und ermöglicht es, bei niedrigeren Spannungen zu funktionieren, was den Stromverbrauch und die Wärmeerzeugung verringert.

In praktischen Anwendungen dient der CMOS -Wechselrichter als grundlegender Baustein für komplexere Logik -Tore und digitale Schaltkreise.Die Immunität mit hoher Rauschen und eine zuverlässige Leistung machen es für Hochgeschwindigkeits- und Präzisionsanwendungen geeignet.Ingenieure entwerfen die NMOS- und PMOS -Transistor -Layout sorgfältig, um die Leistung zu optimieren, wobei die wichtigsten Faktoren wie das thermische Management und die Rauschreduzierung angesprochen werden.Die präzise Transistorpositionierung in einem Wechselrichter -Gate sorgt für eine effiziente Wärmeableitung und minimale Signalinterferenz.

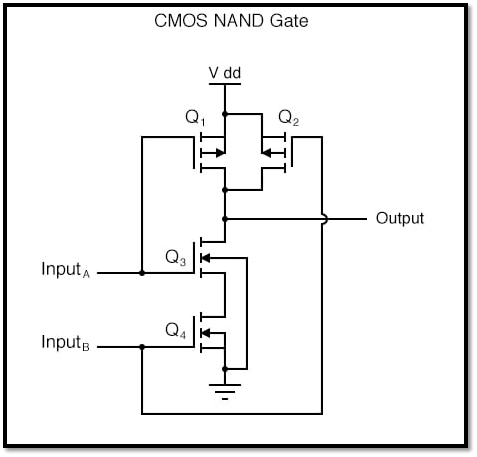

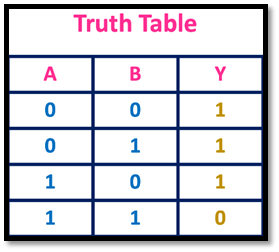

CMOS NAND GATE

Ein CMOS-NAND-Gate wird unter Verwendung einer Kombination aus PMOS-Transistoren (P-Typ-MOS) und NMOs (N-Typ) für optimierte Leistung und Effizienz entwickelt.Es verfügt über zwei PMOS -Transistoren, die parallel zwischen der Stromversorgung (V_DD) und der Ausgabe und zwei NMOS -Transistoren zwischen Ausgang und Masse (V_SS) angeschlossen sind.Dieses Setup gewährleistet einen minimalen Stromverbrauch und eine hohe Immunität mit hoher Rauschen, wodurch die Zuverlässigkeit digitaler Schaltungen verbessert wird.

Abbildung 4: CMOS NAND Gate Schematische Diagramm

Im Schema verwendet das CMOS -NAND -Gate komplementäre PMOS- und NMOS -Transistoren, um die NAND -Logikfunktion auszuführen.Die PMOS -Transistoren (Q1 und Q2) sind in Reihe angeschlossen und halten den Ausgang hoch, wenn entweder der Eingang (a oder b) niedrig ist.Diese Konfiguration zieht den Ausgang nur niedrig, wenn beide Eingänge hoch sind, was das definierende Merkmal eines NAND -Tors ist.

Die NMOS -Transistoren (Q3 und Q4), die parallel angeschlossen sind, ziehen den Ausgang nur dann niedrig, wenn beide Eingänge hoch sind.Dieses Setup stellt sicher, dass die Ausgabe der NAND -Logikfunktion (y = a.b ') folgt, wobei der Ausgang hoch ist, es sei denn, beide Eingänge sind hoch.

Die Verwendung von CMOS -Technologie in diesem Design bietet erhebliche Vorteile, einschließlich geringem Stromverbrauch und Immunität mit hohem Rauschen, wodurch das CMOS -NAND -Gate für verschiedene digitale Anwendungen effizient ist.

Der Betrieb des CMOS Nand Gate wird durch die auf die Transistoren angewendeten Eingangssignale bestimmt.Das Verhalten des Gate kann durch seine Wahrheitstabelle für eine Konfiguration mit zwei Eingängen dargestellt werden:

Abbildung 5: CMOS -NAND -GATE -Wahrheitstabelle

Wenn beide Eingänge (A und B) niedrig sind (0), sind beide NMOS -Transistoren ausgeschaltet und beide PMOS -Transistoren sind eingeschaltet, wodurch die Ausgabe mit V_DD verbunden ist, was zu einem hohen Ausgang (y = 1) führt.Der aktuelle Pfad wird über die PMOS -Transistoren abgeschlossen, sodass sich V_DD an die Ausgabe ausbreiten kann.

Wenn entweder der Eingang (A oder B) niedrig ist (0), ist mindestens ein NMOS -Transistor ausgeschaltet, wodurch die PMOS -Transistoren die Ausgabe an V_DD verbinden, was ebenfalls zu einem hohen Ausgang (y = 1) führt.Diese Redundanz stellt sicher, dass das Tor seinen hohen Ausgang beibehält, selbst wenn ein Pfad unterbrochen wird.

Wenn beide Eingänge (A und B) hoch sind (1), sind beide NMOS -Transistoren eingeschaltet und beide PMOS -Transistoren sind ausgeschaltet, wodurch der Ausgang mit dem Boden verbunden und zu einem niedrigen Ausgang (y = 0) verbunden ist.Dieser Zustand erzeugt einen direkten Weg zum Boden und zieht schnell den Ausgang niedrig.

Dieser Vorgang zeigt die Effektivität des CMOS Nand Gate bei der Ausführung logischer Funktionen mit minimaler Stromversorgung und hoher Zuverlässigkeit.

Das CMOS NAND Gate ist ein universelles Tor mit vielseitigen Anwendungen in verschiedenen Bereichen:

CMOS -NAND -Gates können jede Boolesche Funktion implementieren und als grundlegende Bausteine für den Bau anderer Logik -Gates und komplexer Schaltungen dienen.

Wird in grundlegenden Logikfunktionen und Schaltungen wie Addierern, Subtrahieren und Multiplexern verwendet.

Schlüssel zum Entwerfen von Flip-Flops, Riegel und anderen Speicherelementen, wodurch der Zustand der Status und den Übergang in aufeinanderfolgenden sequentiellen Schaltungen ermöglicht wird.

Kombinieren Sie mehrere Kontrollsignale und bestimmen Sie Systemaktionen, um sicherzustellen, dass ineinandergreifende Systeme mehrere Bedingungen erfüllen, damit eine Aktion auftritt.

Wird zur Gestaltung von statischen RAM (SRAM) -Zellen und zur Verwaltung von Kontrollsignalen für die Datenintegrität verwendet.

Fehlererkennung und Korrektur: Mechanismen wie Paritätsprüfer und Generatoren, die zuverlässige und fehlerfreie Datenübertragung und -betrieb in Redundanzsystemen sicherstellen.

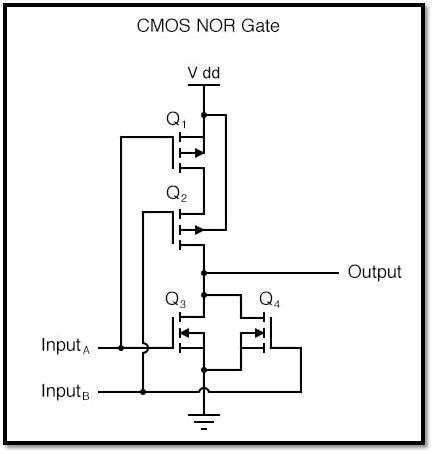

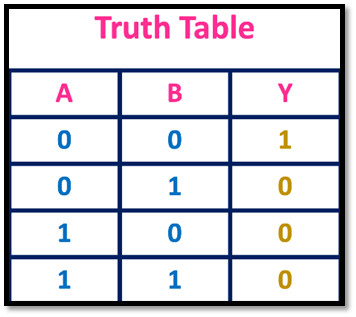

CMOS oder Tor

Erforschen Sie die komplizierten Details einer der Schlüsselkomponenten im modernen digitalen Logikdesign, dem CMOS oder Gate.In diesem Abschnitt wird das Design, den Betrieb und die Anwendungen des CMOS NOR-GATE abgebaut, wodurch seine Rolle bei der Schaffung effizienter, zuverlässiger und digitaler Systeme mit geringer Leistung hervorgehoben wird.

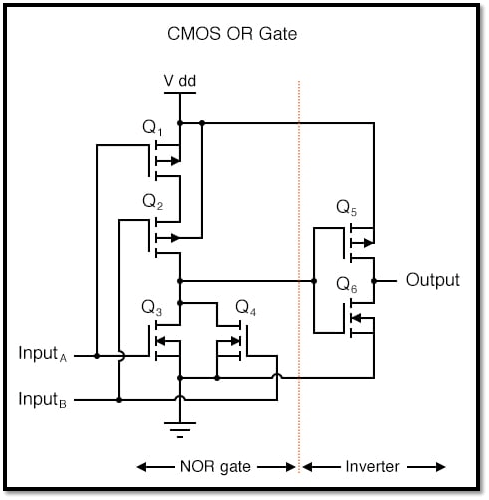

Das CMOS Nor Gate verwendet eine Kombination aus PMOS-Transistoren vom P-Typ (P-Typ) und NMOs (N-Typ).In der Regel umfasst das Design zwei PMOS -Transistoren, die parallel zwischen der Stromversorgung (V_DD) und dem Ausgang und zwei NMOS -Transistoren zwischen Ausgang und Masse (V_SS) angeschlossen sind.

Abbildung 6: CMOS- oder Gate -Schematikramm

In dieser Konfiguration ziehen die PMOS -Transistoren (Q1 und Q2) den Ausgang hoch, wenn beide Eingänge (Eingang A und Eingang B) niedrig sind.Dieses Setup stellt sicher, dass der Ausgang hoch bleibt, es sei denn, eine oder beide Eingänge sind hoch.Die NMOS -Transistoren (Q3 und Q4), die in Serie angeschlossen sind, ziehen den Ausgang niedrig, wenn der Eingang hoch ist.Wenn beide Eingänge niedrig sind, leisten Q3 und Q4 nicht, sodass die PMOS -Transistoren einen hohen Ausgang aufrechterhalten können.Dieses Design führt effektiv die NOR -Logikfunktion (y = a + b) aus, wobei der Ausgang niedrig ist, wenn der Eingang hoch ist.Die Effizienz und Zuverlässigkeit dieses Designs wird durch den geringen Stromverbrauch und die robuste Leistung der CMOS -Technologie verbessert.

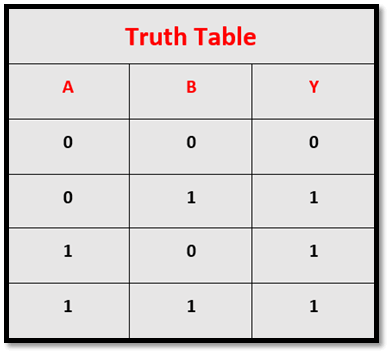

Der Betrieb des CMOS oder Gate basiert auf den auf die Transistoren angewendeten Eingangssignale.Das Verhalten des Gate kann durch seine Wahrheitstabelle für eine Konfiguration mit zwei Eingängen verstanden werden:

Wenn beide Eingänge (A und B) niedrig sind (0), sind beide NMOS -Transistoren ausgeschaltet und beide PMOS -Transistoren sind eingeschaltet, wobei die Ausgabe mit V_DD verbunden ist und zu einem hohen Ausgang (y = 1) führt.In diesem Zustand ermöglicht das Fehlen eines Strompfads zum Boden die Spannung, sich durch die PMOS -Transistoren zu vermehren.

Abbildung 7: CMOS oder Gate -Wahrheitstabelle

Wenn entweder der Eingang (A oder B) hoch (1) ist, ist mindestens ein NMOS -Transistor eingeschaltet, wodurch ein direkter Weg zum Boden erzeugt wird und zu einem niedrigen Ausgang (y = 0) führt.Gleichzeitig ist mindestens ein PMOS -Transistor ausgeschaltet und unterbricht die Verbindung zwischen V_DD und der Ausgabe.

Wenn beide Eingänge hoch sind (1), sind beide NMOS -Transistoren eingeschaltet und beide PMOS -Transistoren sind ausgeschaltet, um eine starke Verbindung zum Boden und eine niedrige Ausgabe zu gewährleisten (y = 0).

Dieser Vorgang unterstreicht die Fähigkeit des Nor Gate, logische Funktionen effizient und zuverlässig mit minimaler Stromversorgung auszuführen.

Die Vielseitigkeit des CMOS Nor Gate zeigt sich in seinem breiten Anwendungsbereich:

Wird verwendet, um verschiedene kombinations- und sequentielle Logikschaltungen zu erstellen und als grundlegende Baustein in der logischen Synthese und des Schaltungsdesigns zu dienen.

Sehr wichtig für die Gestaltung von SRAM- und DRAM -Zellen ist der geringe Stromverbrauch und die hohe Rauschimmunität ihre Vorteile.Die Effizienz des Schaltbetriebs verbessert die Datenbindung und die Zugriffsgeschwindigkeit.

Integraler Bestandteil der Funktionsweise von Alus, Steuereinheiten und anderen Komponenten.Die Effizienz und Zuverlässigkeit des Gate machen es für diese komplexen Systeme unerlässlich.

CMOs und Tor

Dieser Teil bietet einen detaillierten Blick auf eine der Schlüsselkomponenten im digitalen Logikdesign, das CMOS und das Gate.In diesem Abschnitt werden die Designprinzipien, Schaltpläne, Betriebsdetails und verschiedene Anwendungen der CMOs und des Gate untersucht.

Das Design eines CMOS und eines Gate umfasst die sorgfältige Anordnung von NMO- und PMOS-Transistoren in zwei Hauptteilen: das Pulldown-Netzwerk (PDN) und das Pull-up-Netzwerk (PRW).Die PDN, die aus NMOS -Transistoren hergestellt wird, die in Reihe angeschlossen sind, zieht den Ausgang auf den Boden, wenn beide Eingänge A und B hoch sind.Das Wortspiel, das parallel aus PMOS -Transistoren besteht, zieht den Ausgang an die Versorgungsspannung (VDD), wenn der Eingang niedrig ist.

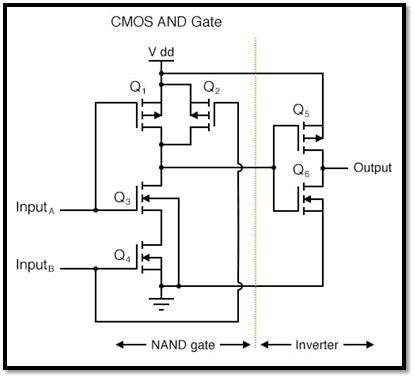

Abbildung 8: CMOS- und Gate -Schematikramm

Im CMOS und Gate ziehen PMOS -Transistoren (Q1 und Q2) den Ausgang hoch, wenn einer der Eingänge niedrig ist, und stellt sicher, dass der Ausgang hoch bleibt, es sei denn, beide Eingänge sind hoch.NMOS -Transistoren (Q3 und Q4) ziehen den Ausgang nur dann niedrig, wenn beide Eingänge hoch sind und die und Funktion ausführen.

Um die und Funktionalität zu erreichen, verwendet das Design ein NAND -Tor, gefolgt von einem Wechselrichter.Das NAND -Gate aus Q1, Q2, Q3 und Q4 erzeugt eine niedrige Ausgabe, wenn beide Eingänge hoch sind.Dieser Ausgang wird durch die Wechselrichterstufe (Q5 und Q6) umgekehrt, die das Signal umdreht, um die endgültige und den Ausgang zu liefern.Diese Anordnung stellt sicher, dass der Ausgang nur hoch ist, wenn beide Eingänge hoch sind und sich mit der und Logik ausrichten.Das Design ist in Bezug auf Stromverbrauch und Geschwindigkeit effizient, die für die CMOS -Technologie charakteristisch ist, und wird in digitalen Schaltkreisen, die Zuverlässigkeit und geringem Stromverbrauch erfordern, häufig eingesetzt.

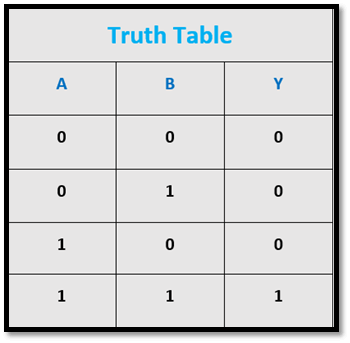

Der Betrieb der CMOs und des Gate wird durch die auf die Transistoren angewendeten Eingangssignale bestimmt.Das Verhalten des Gate wird durch seine Wahrheitstabelle für eine Konfiguration mit zwei Eingängen beschrieben:

Abbildung 9: CMOs und Gate -Wahrheitstabelle

Beide Eingänge sind niedrig (a = 0, b = 0): Beide NMOS -Transistoren sind ausgeschaltet und beide PMOS -Transistoren sind eingeschaltet.Dieser Zustand zieht den Ausgang auf den Boden, was zu einem niedrigen Ausgang (y = 0) führt.Die Bodenverbindung verhindert, dass Strom durch die PMOS -Transistoren fließt.

Ein Eingang niedrig, einer hoch (a = 0 oder b = 0): Mindestens ein NMOS -Transistor ist ausgeschaltet und hält den Ausgang niedrig.Diese Bedingung stellt sicher, dass das Gate einen niedrigen Ausgang beibehält, solange jeder Eingang niedrig ist.

Beide Eingaben sind hoch (a = 1, b = 1): Beide NMOS -Transistoren sind eingeschaltet und beide PMOS -Transistoren sind ausgeschaltet.Dadurch kann die Ausgabe eine Verbindung zu V_DD herstellen, was zu einer hohen Ausgabe (y = 1) führt.Der Strompfad durch die NMOS -Transistoren stellt sicher, dass die Ausgangsspannung hoch gezogen wird.

In praktischer Hinsicht kann ein Ingenieur das CMOS und das Gate auf einem Breadboard testen.Anschließend die Gate -Eingänge mit einer doppelten Stromversorgung (0 V für niedrig, 5 -V für hohe) verwendet der Ingenieur ein Oszilloskop, um den Ausgang zu überwachen.Bei beiden Eingängen bei 0 V zeigt das Oszilloskop 0 V am Ausgang und bestätigt einen niedrigen Ausgang.Wenn Sie einen Eingang auf 5 V einstellen, während die andere bei 0V bei 0V bei 0V aufbewahrt wird, bestätigt sie die Logik.Wenn Sie beide Eingänge auf 5 V einstellen, wird der Ausgang auf 5 V gesunken, wodurch der Betrieb des Gate überprüft wird.

Das CMOS und das Gate sind in verschiedenen Anwendungen in großem Umfang im digitalen Logikdesign verwendet:

Erforderlich zum Erstellen von Kombinationslogikschaltungen wie Addierern, Subtrahieren und Multiplexern sowie sequentiellen Logikschaltungen wie Flip-Flops, Zähler und Registern.

Hilft bei der Auswahl der Daten und der Rauschfilterung und stellt sicher, dass nur gewünschte Signale verarbeitet werden.

Erleichtert Entscheidungsprozesse und Subsystem-Schnittstellen, bei denen mehrere Bedingungen erfüllt werden müssen, damit bestimmte Maßnahmen erfolgen.

Verwaltet die Datenübertragung, Codierung und Dekodierung und unterstützt die Mechanismen für Fehlererkennung und Korrektur, um die Datenintegrität sicherzustellen.

Wird in Ausführungseinheiten zur Durchführung logischer Operationen und in der Kontrolllogik zur Koordinierung des Datenflusss verwendet.

Leistungsmanagement: Steuert die Leistungsverteilung und reguliert die Spannungsniveaus, wodurch der effiziente Systembetrieb und die selektive Leistung von Komponenten sichergestellt werden.

Die CMOs und das Gate mit seiner zuverlässigen und effizienten Leistung sind ein wesentlicher Bestandteil der Entwicklung moderner digitaler Systeme und bieten einen geringen Stromverbrauch und einen Hochgeschwindigkeitsbetrieb.

CMOs oder Tore

Ein CMOS oder ein Gate wird sowohl mit PMOS- als auch mit NMOS-Transistoren entwickelt, um einen geringen Stromverbrauch und Hochgeschwindigkeitsleistung zu erzielen.Das Gate hat zwei Eingänge, A und B und einen Ausgang, Y. Der Ausgang y ist hoch (1) Wenn entweder Eingang a oder Eingang B hoch ist, folgt dem logischen Ausdruck y = A + B.

Abbildung 10: CMOS oder GATE -Schema -Diagramm

In diesem Design sind zwei PMOS -Transistoren (P1 und P2) parallel zwischen der Versorgungsspannung (VDD) und dem Ausgang Y angeschlossen. Das Gate von P1 ist an Eingang A angeschlossen, und das Gate von P2 ist mit Eingang B.NMOS -Transistoren (Q3 und Q4) sind in Reihe zwischen Ausgang und Masse (GND) angeschlossen.Das Gate von Q3 ist mit Eingang A angeschlossen, und das Tor von Q4 ist mit Eingang B verbunden. Der Ausgang ist hoch (1), wenn mindestens einer der Eingänge (a oder b) hoch ist.Die PMOS -Transistoren ziehen den Ausgang hoch, wenn der Eingang niedrig ist, während die NMOS -Transistoren den Ausgang niedrig ziehen, wenn beide Eingänge niedrig sind.Diese Konfiguration gewährleistet einen effizienten Umschalten mit minimalem Stromverbrauch, ein Merkmal der CMOS -Technologie.

Die interne Struktur umfasst auch ein Nor -Gate, gefolgt von einem Wechselrichter, um die oder Funktionalität zu erreichen.Das Nor -Gate, das durch Q1, Q2, Q3 und Q4 gebildet wird, erzeugt nur, wenn beide Eingänge hoch sind.Diese Ausgabe wird dann durch Q5 und Q6 invertiert und liefert die endgültige oder Ausgabe.Dieses Design sorgt für hohe Rauschen und niedrigen statischen Stromverbrauch und ist für verschiedene digitale Logikanwendungen geeignet.

Abbildung 11: CMOS oder Gate -Wahrheitstabelle

Der Betrieb des CMOS oder des Gate kann durch seine Wahrheitstabelle für eine Konfiguration mit zwei Eingängen verstanden werden:

Wenn beide Eingänge (A und B) niedrig sind (0), sind beide NMOS -Transistoren ausgeschaltet und beide PMOS -Transistoren sind eingeschaltet, wodurch der Ausgang auf den Boden gezogen wird, was zu einem niedrigen Ausgang (y = 0) führt.

Wenn entweder der Eingang (A oder B) hoch (1) ist, ist mindestens ein PMOS -Transistor ausgeschaltet und mindestens ein NMOS -Transistor ist eingeschaltet, wobei der Ausgang an V_DD gezogen wird, was zu einem hohen Ausgang (y = 1) führt.

Wenn beide Eingänge (A und B) hoch sind (1), sind beide PMOS -Transistoren ausgeschaltet und beide NMOS -Transistoren sind eingeschaltet, wodurch die Ausgabe an V_DD gezogen wird, was zu einem hohen Ausgang (y = 1) führt.

In der Praxis würde ein Ingenieur, der das CMOS oder das Gate auf einem Störbrett testet, die Eingänge mit einer doppelten Stromversorgung anschließen, die 0 V für niedrige und 5 -V -Hochstoffe für hoch sorgt.Mit einem Oszilloskop beobachtete der Ingenieur den Ausgang.Bei beiden Eingängen bei 0V zeigt der Ausgang 0V.Wenn Sie einen Eingang auf 5 V einstellen, während der andere bei 0 V die Ausgabe auf 5 V ändert.

Durch das Einstellen von beiden Eingängen auf 5 V wird die Ausgabe bei 5 V beibehalten, wodurch der Betrieb des Gate bestätigt wird.

Das CMOS oder das Gate ist für das Design der digitalen Schaltung, die Signalverarbeitung, die Steuerungssysteme, die Kommunikationssysteme, das Design von Mikroprozessors und das Leistungsmanagement von wesentlicher Bedeutung.

Im Digital Circuit Design werden CMOs oder Gates verwendet, um Kombinationslogikschaltungen wie Multiplexer, Demultiplexer und arithmetische Logikeinheiten (ALUS) sowie sequentielle Logikschaltungen wie Flip-Flops und Zähler für die Datenspeicherung und -verarbeitung zu erstellen.

In der Signalverarbeitung kombinieren CMOs oder Gates mehrere Datenströme und unterstützen die Datenrouting und die Rauschfilterung, um die Klarheit und Genauigkeit zu verbessern.Kontrollsysteme verwenden diese Gates für Entscheidungsprozesse basierend auf mehreren Eingabedingungen, um die ordnungsgemäße Signalinterpretation und -akte zu gewährleisten.

In Kommunikationssystemen verwalten CMOs oder Gates die Datenübertragung, erleichtern die Fehlererkennung und -korrektur und spielen eine Rolle bei der Signalmodulation und Demodulation.Das Mikroprozessordesign verwendet diese Gates für logische Vorgänge, die für die Ausführung des Anweisungen und die Steuerung des Datenflusss und des Zeitpunkts erforderlich sind.

Bei der Stromversorgung werden CMOs oder Gates im Stromversand verwendet, um die Leistungsverteilung zu steuern, selektiv Stromkomponenten und Spannungsstufen zu verwalten, um einen sicheren und optimalen Betrieb zu gewährleisten.

CMOS XOR GATE

Das CMOS XOR -Gate ist für das moderne digitale Logikdesign von grundlegender Bedeutung, das für die Erzeugung eines hohen Ausgangssignals bekannt ist, wenn sich seine beiden Eingänge unterscheiden.In diesem Abschnitt wird die Entwurf, den Betrieb und die vielseitigen Anwendungen beschrieben und seine wichtige Rolle bei elektronischen Schaltkreisen hervorgehoben.

Entwurf des CMOS XOR -Tores

Bei der Gestaltung eines CMOS XOR-GATE wird die Verwendung von PMOS- und NMOS-Transistoren für den Stromverbrauch mit geringem Stromverbrauch und Hochgeschwindigkeitsleistung verwendet.Das XOR -Tor verfügt über zwei Eingänge, A und B und einen Ausgang, Y. Das Ausgang y ist hoch (1), wenn entweder A oder B hoch ist, aber nicht beides, folgt dem logischen Ausdruck y = a ⊕ B.

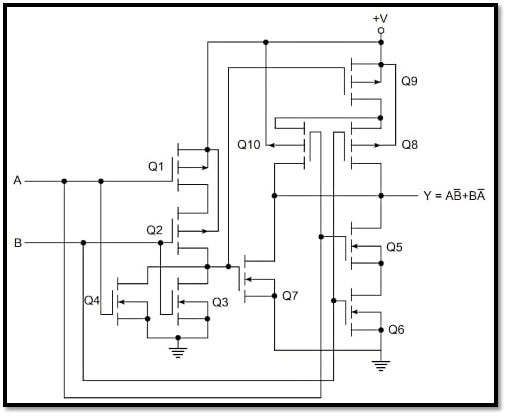

Abbildung 12: CMOS XOR GATE Schematische Diagramm

Das Pull-up-Netzwerk (Wortspiel) von PMOS-Transistoren zieht den Ausgang hoch, wenn ein Eingang hoch ist und der andere niedrig ist.Umgekehrt zieht das Pulldown-Netzwerk (PDN) von NMOS-Transistoren den Ausgang niedrig, wenn beide Eingänge entweder hoch oder niedrig sind.

Im schematischen Transistoren (Q1 bis Q5) und NMOS -Transistoren (Q6 bis Q10) sind angeordnet, um die XOR -Logik zu erreichen.Die PMOS -Transistoren ziehen den Ausgang hoch, wenn sich die Eingänge unterscheiden, während die NMOS -Transistoren ihn niedrig ziehen, wenn die Eingänge gleich sind.Dieses Design sorgt für einen effizienten Betrieb mit geringem Stromverbrauch und hoher Rauschimmunität, wesentlicher Vorteile der CMOS -Technologie.

Betrieb des CMOS XOR -Tores

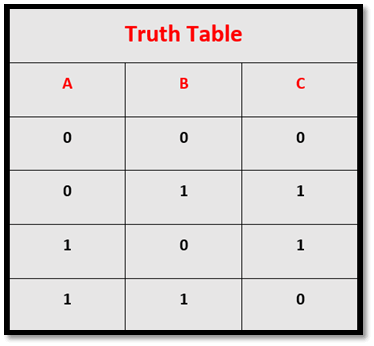

Der Betrieb des CMOS XOR-Gate wird durch seine Wahrheitstabelle für eine Konfiguration mit zwei Eingängen definiert:

Abbildung 13: CMOS XOR GATE TRUET TABELLE

Wenn beide Eingänge (a und b) niedrig sind (0), ist der Ausgang niedrig (y = 0).

Wenn die Eingabe a niedrig ist (0) und die Eingabe B hoch (1) oder Eingang A hoch (1) und Eingang B niedrig (0) ist, ist der Ausgang hoch (y = 1).

Wenn beide Eingänge hoch sind (1), ist der Ausgang niedrig (y = 0).

Dieses Verhalten wird durch die sorgfältige Anordnung von CMOS -Transistoren erreicht, die unterschiedliche logische Zustände effektiv verarbeiten.

Praktisch verbindet ein Ingenieur, der das CMOS XOR -Gate auf einem Steckbrett testet, die Eingänge mit einer doppelten Stromversorgung (0V für niedrig, 5 V für hoch).Mit einem Oszilloskop zur Überwachung des Ausgangs stellt der Ingenieur beide Eingänge auf 0V oder 5 V und zeigt eine konstante 0 V am Ausgang an.Wenn Sie einen Eingang auf 5 V einstellen, während der andere bei 0 V die Ausgabe auf 5 V ändert.Diese Schritt-für-Schritt-Validierung bestätigt den Betrieb des Gate.

Anwendungen von CMOS XOR GATE

Das CMOS XOR-Gate ist aufgrund seines geringen Stromverbrauchs und seiner Hochgeschwindigkeitsleistung von wesentlicher Bedeutung für das digitale Logikdesign, was es in verschiedenen Anwendungen häufig verwendet hat.

In arithmetischen Schaltungen berechnen CMOS XOR -Gates Summenbits in Addern.Sie sind entscheidend für die Erkennung und Korrektur von Fehler, Generieren und Überprüfung von Paritätsbits sowie zur Implementierung von CRC- und Hamming -Code -Algorithmen.

In der Kryptographie kombinieren CMOS XOR -Gates Klartext mit Tasten für die sichere Datenverschlüsselung und Entschlüsselung.Sie sind integraler Bestandteil von Signalmodulation, Frequenzmischung und digitalen Modulationsschemata, wodurch die Signalverarbeitungsfunktionen verbessert werden.

In Kontrollsystemen ermöglichen CMOS XOR-Gates Entscheidungsfunktionen und Umschaltfunktionen.In Mikroprozessoren unterstützen sie aufgrund ihrer Effizienz und Geschwindigkeit logische und bitweise Vorgänge.Darüber hinaus optimieren CMOS XOR -Gates den Stromverbrauch und regulieren die Spannungsniveaus im Stromverwaltung, wodurch zur Effizienz und Zuverlässigkeit des Gesamtsystems beiträgt.Ihre Vielseitigkeit und Leistung machen CMOS XOR Gates im modernen elektronischen Design von Bedeutung.

Abschluss

Die CMOS -Technologie hat das digitale Logikdesign revolutioniert, indem die ergänzende Natur von NMOs- und PMOS -Transistoren eingesetzt wird.Diese Kombination erzielt eine hohe Leistung mit minimalem Stromverbrauch und macht CMOS -Schaltkreise für moderne elektronische Geräte von entscheidender Bedeutung.Die CMOS -Technologie ist die Grundlage für verschiedene digitale Schaltkreise, von einfachen Wechselrichtern bis hin zu komplexen Toren wie Nand, Nor und, OR und XOR.Es fördert Innovationen in Prozessoren, Speicher und zahlreichen elektronischen Anwendungen.Das genaue Design und seine operative Effizienz gewährleisten robuste, zuverlässige und energieeffiziente Systeme.Mit dem Fortschritt der digitalen Technologie formt CMOs weiterhin die Zukunft des elektronischen Designs und unterstützt die Entwicklung hoch entwickelter und effizienter Geräte.

Häufig gestellte Fragen [FAQ]

1. Was ist der Unterschied zwischen CMOS -Logik -Toren und grundlegenden Logik -Toren?

CMOS -Logik -Gates unterscheiden sich von den grundlegenden Logik -Toren hauptsächlich in der Konstruktion und der Stromversorgung.CMOS -Gates verwenden sowohl NMOS- als auch PMOS -Transistoren, die komplementär betrieben werden, und stellt sicher, dass nur eine Art von Transistor gleichzeitig durchgeführt wird.Dieses Design minimiert den Stromverbrauch, insbesondere die statische Leistung, da der Strom nur während des Wechsels Ereignisse fließt.Im Gegensatz dazu basieren grundlegende Logik-Gates, die häufig mit TTL-Technologie (Transistor-Transistor-Logik) gebaut wurden, bipolare Übergangtransistoren und konsumieren mehr Leistung, selbst wenn sie nicht wechseln, aufgrund einer höheren statischen Stromversorgung.Darüber hinaus bieten CMOS-Gates eine bessere Geräuschimmunität und kann bei niedrigeren Spannungen arbeiten, was sie für moderne integrierte Schaltkreise mit hoher Dichte geeignet ist.Diese Qualitäten schaffen die CMOS -Technologie als bevorzugten Ansatz für das zeitgenössische digitale Logikdesign.

2. Wie trägt die CMOS -Technologie zur Miniaturisierung und Effizienz moderner elektronischer Geräte bei?

Die CMOS -Technologie spielt eine wichtige Rolle bei der Miniaturisierung und Verbesserung der Effizienz moderner elektronischer Geräte.Durch die Integration von NMO- und PMOS-Transistoren in einen einzelnen Chip ermöglicht die Platzierung von Transistoren mit hoher Dichte, wodurch die Größe der Komponenten verringert wird.Diese Technologie minimiert den Stromverbrauch und die Wärmeerzeugung, was für batteriebetriebene Geräte wie Smartphones und Laptops von entscheidender Bedeutung ist.CMOS-Schaltkreise nutzen die Stromversorgung hauptsächlich während staatlicher Übergänge, was sie perfekt für Anwendungen mit geringer Leistung perfekt macht.Darüber hinaus gewährleistet die genaue Kontrolle von CMOS über Transistorzustände eine effiziente Leistung und trägt zur Entwicklung fortschrittlicher Prozessoren und Speichereinheiten bei.Diese Faktoren stellen die CMOS -Technologie als grundlegend für die Schaffung kleinerer, effizienterer elektronischer Geräte fest.

3. Was sind die Hauptvorteile der Verwendung der CMOS -Technologie im digitalen Logikdesign?

Die CMOS -Technologie bietet mehrere Vorteile des digitalen Logikdesigns, einschließlich geringem Stromverbrauch, Immunität mit hoher Rausch und der Fähigkeit, bei niedrigeren Spannungen zu arbeiten.Diese Funktionen machen CMOs für batteriebetriebene Geräte und Hochgeschwindigkeitsanwendungen geeignet.CMOS -Schaltkreise konsumieren hauptsächlich während des Schaltens Strom, was zu einer minimalen statischen Stromversorgung führt.Eine hohe Rauschenimmunität sorgt selbst in verrückten Umgebungen zuverlässig, während der Betrieb mit niedrigem Spannung die Akkulaufzeit in tragbaren Geräten verlängert.Diese Attribute machen CMOS -Schaltungen robust, zuverlässig und effizient, die für die Entwicklung fortschrittlicher und zuverlässiger elektronischer Systeme erforderlich sind.

4. Wie funktionieren CMOS -Wechselrichter und warum sind sie im digitalen Logikdesign von Bedeutung?

CMOS -Wechselrichter spielen eine wichtige Rolle im digitalen Logikdesign und dienen als Kernbausteine.Sie verwenden einen mit dem Boden verbundenen NMOS -Transistor und einen PMOS -Transistor, der mit der Stromversorgung verbunden ist.Wenn der Eingang hoch ist, aktiviert der NMOS -Transistor und zieht den Ausgang niedrig.Wenn der Eingang niedrig ist, aktiviert der PMOS -Transistor und zieht den Ausgang hoch.Dieser effiziente Schaltmechanismus minimiert den Stromverbrauch.CMOS-Wechselrichter sind erforderlich, um komplexere Logik-Gates und -kreise zu konstruieren, wodurch eine zuverlässige und energieeffiziente Signalinversion für digitale Geräte wie Mikroprozessoren und Speichereinheiten erforderlich ist.

5. Können Sie die Bedeutung von CMOS NAND und NOR -Toren für die digitale Elektronik erklären?

CMOS NAND und NOR GATE spielen aufgrund ihrer Effizienz und Vielseitigkeit eine wesentliche Rolle bei der digitalen Elektronik.CMOS -NAND -Gates verwenden PMOS -Transistoren parallel und NMOS -Transistoren in Reihe, um einen geringen Stromverbrauch und eine hohe Rauschimmunität zu gewährleisten, die für Speicherchips und Mikroprozessoren signifikant sind.CMOS Nor Gates mit PMOS -Transistoren in Reihe und NMOS -Transistoren können parallel wesentliche Logikfunktionen in digitalen Steuerungssystemen ausführen.Beide Gates sind von grundlegender Bedeutung für die Erstellung von kombinations- und sequentiellen Logikkreisen und verbessern die allgemeine Zuverlässigkeit und Effizienz integrierter Schaltungen in verschiedenen digitalen Geräten.

Verwandter Artikel

-

Jun 21 2024Universelle Gates: Die Grundlagen des zeitgenössischen digitalen Logikdesigns

Entdecken Sie die transformativen Auswirkungen von universellen Toren in der digitalen Elektronik, indem Sie unseren eingehenden Artikel über NAND un... -

Jun 19 2024Umfassende Anleitung zu NPN- und PNP -Transistoren

Schalte die Geheimnisse von Transistoren mit unserem umfassenden Leitfaden frei.Dieser Leitfaden untersucht die faszinierende Welt der Transistoren un...

Verwandte -Produkte

SMAJ33A

TVS DIODE 33VWM 53.3VC SMA

XCV100-5PQ240I

IC FPGA 166 I/O 240QFP

TMS320C6712DGDP150

IC DSP FLOATING POINT 272-BGA

UPD5100G

NEC QFP

AD7520LN

AD7520LN AD

ST72C216/OBO

ST72C216/OBO ST

UPD720130F1

UPD720130F1 NEC

PCIMX6X3EV010AA

PCIMX6X3EV010AA FREESCALE

T491C105K050ZTZV11Z012

CAP TANT 1UF 10% 50V 2312

G2RL-24DC24

G2RL-24DC24 OMRONELEC

MAX17050X-C08+T10

MAXIM BGA

ERJ2RKF2802X

Relevanzprodukte

12103G684ZAT2A

CAP CER 0.68UF 25V Y5V 1210

vorrätig: 235