- Deutsch

-

EnglishDeutschItaliaFrançais日本語한국의русскийSvenskaNederlandespañolPortuguêspolskiSuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикAfrikaansIsiXhosaisiZululietuviųMaoriKongeriketМонголулсO'zbekTiếng ViệtहिंदीاردوKurdîCatalàBosnaEuskeraالعربيةفارسیCorsaChicheŵaעִבְרִיתLatviešuHausaБеларусьአማርኛRepublika e ShqipërisëEesti Vabariikíslenskaမြန်မာМакедонскиLëtzebuergeschსაქართველოCambodiaPilipinoAzərbaycanພາສາລາວবাংলা ভাষারپښتوmalaɡasʲКыргыз тилиAyitiҚазақшаSamoaසිංහලภาษาไทยУкраїнаKiswahiliCрпскиGalegoनेपालीSesothoТоҷикӣTürk diliગુજરાતીಕನ್ನಡkannaḍaमराठी

dsPIC erhält zwei schnelle 16-Bit-Kerne, um die Entwicklung von Hochleistungs- und Motorsteuerung zu beschleunigen

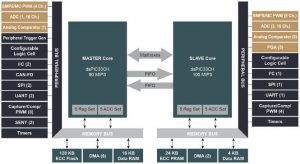

Um die Codeentwicklung zu beschleunigen, indem die Abhängigkeit zwischen Benutzeroberfläche und Echtzeitcode beseitigt wird, sind die Kerne weitgehend unabhängig, haben jeweils eigene Peripheriegeräte und kommunizieren nur über FIFOs und Postfächer miteinander - Daten- und Adressbusse sind dies nicht geteilt.

Innerhalb dsPIC33CHWie die Familie bekannt sein wird, sind die Kerne ähnlich, wobei einer mit 90 MHz als „Master“ und ein „Slave“ mit 100 MHz bezeichnet wird. Der Master verfügt über mehr serielle Schnittstellen, während der Slave beispielsweise über mehr ADCs, PWM-Kanäle und Komparatoren verfügt (siehe Abbildung).

„Der Slave-Core ist nützlich, um dedizierten, zeitkritischen Steuercode auszuführen, während der Master-Core die für die Endanwendung angepassten Funktionen für Benutzeroberfläche, Systemüberwachung und Kommunikation ausführt“, so das Unternehmen. „Der dsPIC33CH wurde speziell entwickelt, um die unabhängige Codeentwicklung für jeden Kern durch separate Designteams zu ermöglichen und eine nahtlose Integration zu ermöglichen, wenn sie auf einem Chip zusammengefasst werden.

Mögliche Anwendungen sind die digitale Energie- und Motorsteuerung, beispielsweise für drahtlose Energieversorgung, Server, Drohnen und Automobilsensoren.

In einem digitalen Netzteil verwaltet laut Microchip der Slave-Kern die mathematikintensiven Algorithmen, während der Master-Kern den PMBus-Protokollstapel unabhängig verwaltet und die Systemüberwachung übernimmt. In einem Fahrzeuglüfter oder einer Fahrzeugpumpe verwaltet der Slave-Kern die zeitkritische Drehzahl- und Drehmomentsteuerung, während der Master die CAN-FD-Kommunikation (CAN-flexible Datenrate) sowie die Systemüberwachung und -diagnose verwaltet.

Live-Firmware-Upgrades (keine Ausfallzeit) sind auf beiden Kernen möglich, da jeder über zwei Flash-Programmspeicher verfügt - insgesamt vier.

Wenn keine Live-Upgrades erforderlich sind, steht dem Core doppelt so viel Programmspeicher zur Verfügung.

Im Vergleich zur vorherigen dsPIC-Familie für denselben Markt - dsPIC33EP / GS - wird die Leistung fast verdoppelt (Latenz von 543ns auf 280ns) - teilweise durch eine Erhöhung der Taktrate von 70MHz auf 100MHz und teilweise durch eine schnellere Kontextumschaltung (kontextsensitive Akkumulatoren) und Statusregister) und neue Anweisungen (schnelleres Teilen, Laden / Speichern mit 32 Bit).

Es gibt acht Gehäusevarianten, vom 28-poligen dsPIC33CH64MP202 bis zu 80-poligen und ab 5 x 5 mm.

Die Flash-Optionen umfassen 64 bis 128 KB.

Unterstützung kommt von:

- MPLAB X IDE

- Code-Konfigurator

- dsPIC33CH Curiosity Board (DM330028)

- dsPIC33CH-Einsteckmodul zur Motorsteuerung (MA330039) für MCLV-2 und MCHV-2/3

- dsPIC33CH-Einsteckmodul für Allzweckplattformen (MA330040) für Explorer 16/32 (DM240001-2)