- Deutsch

-

EnglishDeutschItaliaFrançais日本語한국의русскийSvenskaNederlandespañolPortuguêspolskiSuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикAfrikaansIsiXhosaisiZululietuviųMaoriKongeriketМонголулсO'zbekTiếng ViệtहिंदीاردوKurdîCatalàBosnaEuskeraالعربيةفارسیCorsaChicheŵaעִבְרִיתLatviešuHausaБеларусьአማርኛRepublika e ShqipërisëEesti Vabariikíslenskaမြန်မာМакедонскиLëtzebuergeschსაქართველოCambodiaPilipinoAzərbaycanພາສາລາວবাংলা ভাষারپښتوmalaɡasʲКыргыз тилиAyitiҚазақшаSamoaසිංහලภาษาไทยУкраїнаKiswahiliCрпскиGalegoनेपालीSesothoТоҷикӣTürk diliગુજરાતીಕನ್ನಡkannaḍaमराठी

DAC untersucht die Rolle von KI und ML in den Märkten

Das Moscone Center in San Francisco wird vom 25. bis 28. Juni Gastgeber des DAC sein

OneSpin-Lösungen und Austemper Design Systems werden beide Tools für die Überprüfung der funktionalen Sicherheit hervorheben. Austemper wird sich mit der KaleidoScope-Tool-Suite auf die Entwicklung unternehmenskritischer Systeme konzentrieren, die das analoge Design für die gleichzeitige Fehlerausbreitung bei gemischten Signalen unterstützt. Die automatisierte Tool-Suite bietet Funktionen zur Sicherheitsanalyse, -synthese und -verifizierung für zertifizierungsorientierte Anwendungen. Es wird für große Automobilkonstruktionen in ADAS und für autonomes Fahren verwendet. Die gleichzeitige Fehlersimulation umfasst Simulationen, die von ISO 26262 empfohlen werden, um die ASIL-Anforderungen zu erfüllen.

Das Unternehmen hat sich kürzlich mit OneSpin Solutions zusammengetan, um eine werkzeuggestützte Methodik für Anwendungen der funktionalen Sicherheit zu entwickeln, die einen Entwurfs- und Verifizierungsablauf kombiniert und am OneSpin-Stand demonstriert wird. Hardware-Sicherheitsmechanismen werden in Chip-Designs eingefügt, und die Tools von OneSpin Solutions verifizieren formal die Hardware-Sicherheitslogik. Die Äquivalenzprüfung stellt sicher, dass die eingefügte Sicherheitslogik die normale Funktionalität nicht beeinträchtigt, und die Fehlererkennungsanalyse überprüft, ob die Sicherheitsmechanismen bei zufälligen Fehlern ordnungsgemäß funktionieren.

OneSpin bewirbt auch sein Tool Qualification Kit, nachdem TÜV SÜD seine Tool-Entwicklungsprozesse überprüft hat. Das erste Kit ist für das 360 EC-FPGA EDA-Tool des Unternehmens erhältlich, eine automatische sequenzielle Äquivalenzprüfung, die verhindert, dass FPGA-Entwurfsabläufe zu Implementierungsfehlern führen. Das Kit ist nach ISO 26262, IEC 61508 und EN 50128 zertifiziert.

FPGA-Einblicke

Immer noch mit FPGA-Design, Plunifizieren hat mit Xilinx zusammengearbeitet, um die Vivado-Designsuite in der Cloud über die Plunify Cloud-Plattform anzubieten. Designer zahlen nur 50 Cent für das Kompilieren eines Vivado-Projekts in der Amazon Web Services-Cloud (AWS), einschließlich Lizenzen.

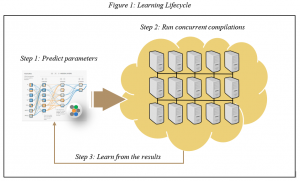

Das Unternehmen wird auch Verbesserungen seiner InTime-Timing-Closure-Software demonstrieren, um das FPGA-Timing in der Cloud zu optimieren (Abbildung 1). Die InTime-Optimierungsmethode kann die Taktfrequenz um 20 bis 80% verbessern und die Zeitanforderungen in Tagen anstatt in Wochen durch maschinelles Lernen erfüllen. Die Software beschleunigt auch das Schließen und Optimieren von Timings und greift über die Cloud zu.

Das Unternehmen wird auch Verbesserungen seiner InTime-Timing-Closure-Software demonstrieren, um das FPGA-Timing in der Cloud zu optimieren (Abbildung 1). Die InTime-Optimierungsmethode kann die Taktfrequenz um 20 bis 80% verbessern und die Zeitanforderungen in Tagen anstatt in Wochen durch maschinelles Lernen erfüllen. Die Software beschleunigt auch das Schließen und Optimieren von Timings und greift über die Cloud zu.

Förderung der eFPGA-Technologie, Achronix Semiconductor arbeitet mit IP-Spezialisten zusammen BESETZUNG um den Durchsatz zu erhöhen und Speicherplatz zu sparen.

Die beiden Aussteller erläutern, wie das verlustfreie CAST-Komprimierungs-IP für den Einsatz in Datencenter- und Mobile-Edge-Datenübertragungsanwendungen in das Achronix-FPGA-Portfolio portiert wurde. Die Hardware-Implementierung des verlustfreien Komprimierungsstandards für Deflate, GZIP und ZLIB ist mit Software-Implementierungen kompatibel, die für die Komprimierung oder Dekomprimierung verwendet werden, um einen Durchsatz von bis zu 100 Gbit / s bei geringer Komprimierung und geringer Latenz zu erzielen Daten bei geringem Stromverbrauch.

CAST hat seine IP auf die FPGAs von Achronix portiert

Energieeffizienz

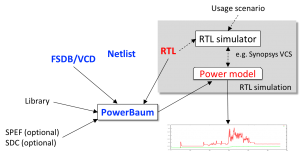

Apropos Power Management, ein weiterer Aussteller, Baumbezeichnet die Energieeffizienz als den am wenigsten entwickelten Bereich im Chip-Design. Das automatisierte Tool zur Leistungsanalyse und -modellierung wurde für Automobil-, IoT-, Mobil-, Netzwerk- und Serverprojekte entwickelt. PowerBaum 2.0 (Abbildung 3) unterstützt dynamische und statische Energie, wobei RTL- und Netzlistenbeschreibungen berücksichtigt werden, und bietet Unterstützung für die Energieanalyse mit Hardware-Emulation. Dies, so das Unternehmen, ermöglicht es den Ingenieuren, Stromversorgungsfehler in realistischen Software-Szenarien zu beheben. Das Tool unterstützt auch die Analyse mit willkürlichen Temperaturen, die von Designern angegeben werden, um die Auswirkungen der Temperatur auf den Energieverbrauch eines Designs zu bewerten.

Auf der DAC wird das Unternehmen auch PowerWurzel vorstellen, eine Leistungsanalyse-Engine auf Gate-Ebene, die für die Leistungsmodellierung in PowerBaum integriert werden soll.

Abbildung 3 Die Tools von Baum analysieren die Energieeffizienz

Cloud-basierte SoC-Design- und Verifikationstools für das IC-Design von Metriken Dazu gehören der Cloud Simulator und der Verification Manager, mit denen die Simulationsanforderungen und -ressourcen verwaltet und jede Minute nach oben oder unten angepasst werden können. Das Unternehmen gibt an, dass Google Cloud eine unbegrenzte UVM-kompatible SystemVerilog-Simulationskapazität und ein natives, webbasiertes Überprüfungsmanagement für schnellere Regressionszeiten, weniger Trunk-Code-Fehler und eine vorhersagbare Codeabdeckung ermöglicht.

Neben den Ausstellern finden auf der Veranstaltung Fachvorträge und ein Programm mit Keynotes zu aktuellen Themen statt. In diesem Jahr wird Cadence beispielsweise ein Tutorial zum Thema "Funktionale Sicherheit und Zuverlässigkeit für Automobilanwendungen" und ein Tutorial zum Thema "Maschinelles Lernen" ("Maschinelles Lernen bringt die Spracherkennungsleistung auf die nächste Stufe") anbieten. Eine Keynote von Anna-Katrina Shedletsky, Instrumental, am Montag, den 25. Juni, befasst sich mit „Automatisierung der Intelligenz: Maschinelles Lernen und die Zukunft der Fertigung“. Der Einsatz von ML und KI für die sozial unterstützte Robotik (Social Assistive Robotics, SAR) wird am Donnerstag in der Keynote von Maja Matarić von der University of Southern California vorgestellt.

Eine weitere Grundsatzrede befürwortet RISC-V, um Architekten von proprietären Befehlssatzarchitekturen (ISAs) zu befreien. David A Patterson, Google und die University of California präsentieren "Ein neues goldenes Zeitalter für Computerarchitektur: domänenspezifische Beschleuniger und Open RISC-V".

Ein neuer Bereich in diesem Jahr bei DAC ist die Design Infrastructure Alley. Die Initiative der ESD-Allianz und Verein für High-Performance-Computing-Profis ist ein Bereich, der der IT-Infrastruktur für das Design elektronischer Systeme und Komponenten gewidmet ist. Neben den Computer- und Speicheranforderungen für das Entwerfen und Verwalten der Cloud-Nutzung gibt es ein spezielles Design-on-the-Cloud-Pavillon-Theater, in dem Lizenzmanagement, Grid-Computing und Datensicherheit behandelt werden.