# **SGMII** and **Gb** Ethernet PCS IP Core

# **User Guide**

FPGA-IPUG-02077-1.6

November 2022

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

### **Contents**

| Acronym  | is in This Document                    | 5  |

|----------|----------------------------------------|----|

| 1. Intro | oduction                               | 6  |

| 1.1.     | Quick Facts                            | 6  |

| 1.2.     | Features                               | 6  |

| 1.3.     | Conventions                            | 7  |

| 1.3.3    | 1. Nomenclature                        | 7  |

| 1.3.2    | 2. Signal Names                        | 7  |

| 1.3.3    | 3. Attribute Names                     | 7  |

| 2. Fund  | ctional Descriptions                   | 8  |

| 2.1.     | Overview                               | 8  |

| 2.2.     | Signal Description                     | 9  |

| 2.3.     | Attribute Summary                      | 12 |

| 2.4.     | Register Description                   | 13 |

| 2.4.3    | 1. Control Register                    | 14 |

| 2.4.2    | 2. Status Register                     | 15 |

| 2.4.3    | 3. Advertised Ability Register         | 15 |

| 2.4.4    | 4. Link Partner Ability                | 16 |

| 2.4.     | 5. Auto Negotiation Expansion Register | 17 |

| 2.4.6    |                                        |    |

| 2.4.     | _                                      |    |

| 2.4.8    | 8. PCS Control Register 0              | 18 |

| 2.4.9    | 9. PCS Control Register 1              | 18 |

| 2.4.3    | -                                      |    |

| 2.4.3    |                                        |    |

| 2.4.3    | 12. PCS Control Register 11            | 20 |

| 2.5.     | Module Description                     |    |

| 2.5.1    | 1. SERDES and PCS                      | 20 |

| 2.5.2    |                                        |    |

| 2.5.3    |                                        |    |

| 2.5.4    | 4. Auto-Negotiation State Machine      | 22 |

| 3. IP G  | Seneration, Simulation, and Validation |    |

| 3.1.     | Generating the IP                      |    |

| 3.2.     | Running Functional Simulation          |    |

| 3.3.     | Constraining the IP                    |    |

| 3.4.     | IP Evaluation                          |    |

| 3.5.     | Hardware Validation                    |    |

| 4. Orde  | ering Part Number                      |    |

|          | x A. Resource Utilization              |    |

|          | res                                    |    |

|          | Support Assistance                     |    |

|          | History                                |    |

|          |                                        |    |

# **Figures**

| Figure 2.1. SGMII/Gb Ethernet PCS IP Top-Level Block Diagram | 8  |

|--------------------------------------------------------------|----|

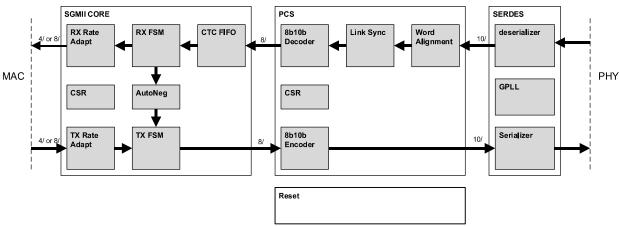

| Figure 2.2. Detailed Block Diagram                           |    |

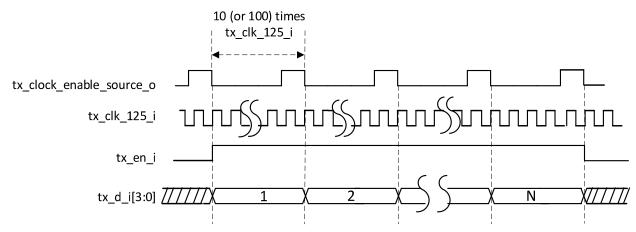

| Figure 2.3. SGMII TX-Side Signals Relationship               | 21 |

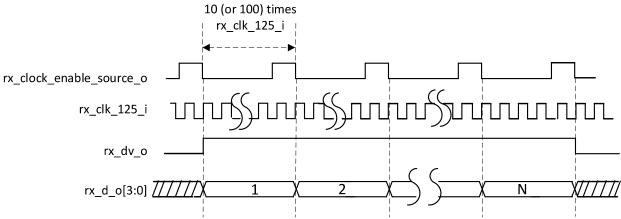

| Figure 2.4. SGMII RX-Side Signals Relationship               | 22 |

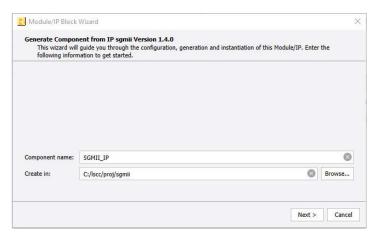

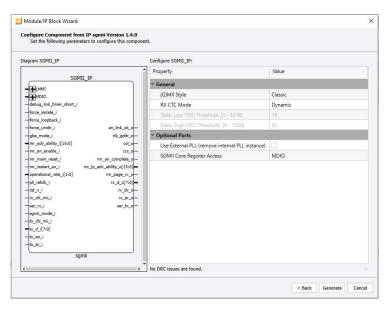

| Figure 3.1. Module/IP Block Wizard                           | 23 |

| Figure 3.2. Configure User Interface of SGMII IP Core        | 23 |

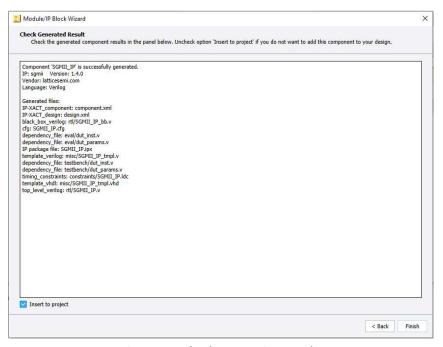

| Figure 3.3. Check Generating Result                          | 24 |

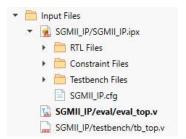

| Figure 3.4. Updated Input Files list                         | 25 |

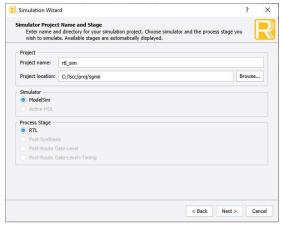

| Figure 3.5. Simulation Wizard                                |    |

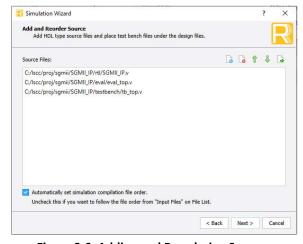

| Figure 3.6. Adding and Reordering Source                     | 25 |

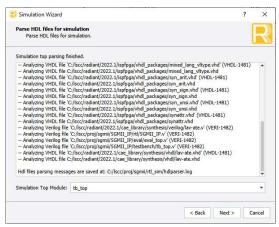

| Figure 3.7. Parse HDL files for simulation                   | 26 |

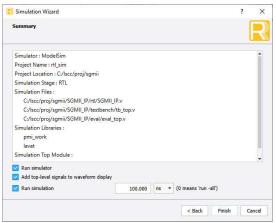

| Figure 3.8. Summary                                          | 26 |

|                                                              |    |

| Tables                                                       |    |

| Table 1.1. SGMII IP Quick Facts                              |    |

| Table 2.1. SGMII IP Core Signal Description                  | g  |

| Table 2.2. Attributes Table                                  | 12 |

| Table 2.3. Attributes Descriptions                           |    |

| Table 2.4. Register Address Map                              | 13 |

| Table 2.5. Access Type Definition                            | 13 |

| Table 2.6. Control Register                                  |    |

| Table 2.7. Status Register                                   | 15 |

| Table 2.8. For PCS=GbE                                       | 15 |

| Table 2.9. For PCS=SGMII-PHY-Side                            | 16 |

| Table 2.10. For PCS=SGMII-MAC-Side                           | 16 |

| Table 2.11. For PCS=GbE                                      | 16 |

| Table 2.12. For PCS=SGMII-PHY-Side                           | 17 |

| Table 2.13. Auto Negotiation Expansion Register              | 17 |

| Table 2.14. Extended Status Register                         | 17 |

| Table 2.15. Configuration Source Control Register            | 17 |

| Table 2.16. PCS Control Register O                           | 18 |

| Table 2.17. PCS Control Register 1                           | 18 |

| Table 2.18. PCS Control Register 9                           | 19 |

| Table 2.19. PCS Control Register 10                          | 19 |

| Table 2.20. PCS Control Register 11                          | 20 |

| Table 3.1. Generated File List                               | 24 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                                 |

|---------|--------------------------------------------|

| СТС     | Clock Tolerance Compensation               |

| FIFO    | First In First Out                         |

| LMMI    | Lattice Memory Mapped Interface            |

| RTL     | Register Transfer Language                 |

| SGMII   | Serial Gigabit Media Independent Interface |

# 1. Introduction

The Serial Gigabit Media Independent Interface (SGMII) connects Ethernet Media Access Controllers (MACs) and Physical Layer Devices (PHYs). This IP core may be used in bridging applications and/or PHY implementations. It is widely used as an interface for a discrete Ethernet PHY chip.

### 1.1. Quick Facts

Table 1.1 shows the summary of the SGMII IP.

**Table 1.1. SGMII IP Quick Facts**

| IP Requirements      | Supported FPGA Families  | CrossLink™-NX, Certus™-NX, CertusPro™-NX, Lattice Avant                                                                                                                                                                                                                         |  |

|----------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | Targeted Devices         | LIFCL-40, LIFCL-17, LFD2NX-40, LFD2NX-17, LFCPNX-100, LFMXO5-25, LAV-AT-500E                                                                                                                                                                                                    |  |

| Resource Utilization | Supported User Interface | (G)MII                                                                                                                                                                                                                                                                          |  |

|                      | Resources                | See Table A.1. Resource Utilization.                                                                                                                                                                                                                                            |  |

| Design Tool Support  | Lattice Implementation   | IP Core v1.0.x – Lattice Radiant™ software 2.1  IP Core v1.1.x - Lattice Radiant software 2.2 and Lattice Propel™  Builder software 2.0  IP Core v1.2.x - Lattice Radiant software 3.0 and Lattice Propel  Builder software 2.0  IP Core v.1.4.x - Lattice Radiant software 3.2 |  |

|                      | Synthesis                | Lattice Synthesis Engine Synopsys® Synplify Pro for Lattice                                                                                                                                                                                                                     |  |

|                      | Simulation               | For a list of supported simulators, see the Lattice Radiant software user guide.                                                                                                                                                                                                |  |

### 1.2. Features

The key features of the SGMII IP include:

- Physical Coding Sublayer (PCS) functions of the Cisco SGMII Specification, Revision 1.8

- PCS functions for IEEE 802.3z (1000BaseX)

- Dynamic selection of SGMII/1000BaseX PCS operation

- Support for MAC or PHY mode for SGMII auto-negotiation

- Support for (G)MII data rates of 1 Gbps, 100 Mbps, 10 Mbps

- Easy Connect option for seamless integration with Lattice Semiconductor's Tri-Speed MAC (TSMAC) IP core

- Management Interface Port for control and maintenance

### 1.3. Conventions

### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.3.2. Signal Names

Signal names that end with:

- \_n are active low (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

### 1.3.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (Attribute Name).

# 2. Functional Descriptions

### 2.1. Overview

SGMII/Gb Ethernet PCS IP core converts GMII frames into 8-bit code groups in both transmit and receive directions and performs auto-negotiation with a link partner as described in the Cisco SGMII and IEEE 802.3z specifications. SGMII IP is a connection bus for MACs and PHYs and is often used in bridging applications and/or PHY implementations. It is particularly widely used as an interface for a discrete Ethernet PHY chip.

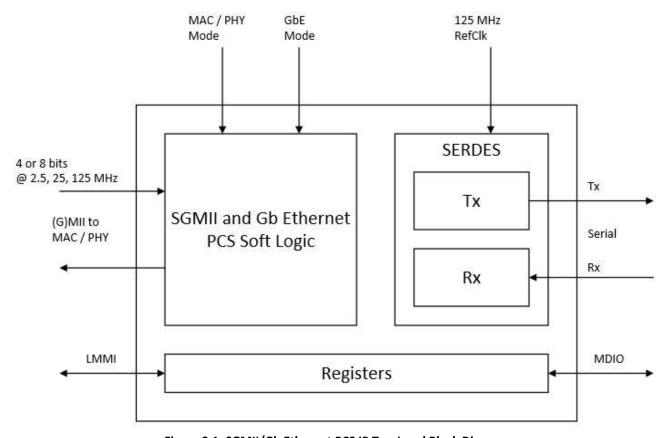

Top-level block diagram of the SGMII IP CORE is shown in Figure 2.1.

Figure 2.1. SGMII/Gb Ethernet PCS IP Top-Level Block Diagram

# 2.2. Signal Description

**Table 2.1. SGMII IP Core Signal Description**

| Port Name                             | 1/0 | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock and Reset                       |     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tx_clk_mii_i                          | In  | 1     | Transmit MII Clock – 125 MHz, 25 MHz, or 2.5 MHz clock for incoming (G)MII transmit data. Data is sampled on the rising edge of this clock. For <i>TSMAC Easy Connect</i> option, this clock is always 125 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tx_clock_enable_source_o <sup>1</sup> | Out | 1     | Transmit Clock Enable Source – This signal is only present when the IP core is generated using the <i>TSMAC Easy Connect</i> (G)MII option. This signal is used in combination with the transmit 125 MHz clock to regulate the flow of transmit (G)MII data. The signal is generated by the transmit rate adaptation block. This clock enable should be tied to the transmit section of the MAC that sends transmit Ethernet frames to the SGMII and Gb Ethernet PCS IP core. This clock enable should also be tied to the clock enable <i>sink</i> of the SGMII and Gb Ethernet PCS IP core. This clock enable's behavior is controlled by the setting of the operational rate pins - operational_rate_i, of the IP core. For 1 Gbps operation, the clock enable is constantly high. For 100 Mbps operation, the clock enable is high for one-out-of-ten 125 MHz clock cycles. For 10 Mbps operation, the clock enable is high for one-out-of-one-hundred 125 MHz clock cycles. <sup>1</sup> |

| tx_clock_enable_sink_i <sup>1</sup>   | In  | 1     | Transmit Clock Enable Sink – This signal is only present when the IP core is generated using the <i>TSMAC Easy Connect</i> (G)MII option. This signal is used in combination with the transmit 125 MHz clock to regulate the flow of transmit (G)MII data. When the clock enable is high and the transmit clock edge rises, (G)MII data is sampled. <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rx_clk_mii_i                          | In  | 1     | Receive MII Clock – 125 MHz, 25 MHz, or 2.5 MHz clock for outgoing (G)MII receive data. Data is launched on the rising edge of this clock. For <i>TSMAC Easy Connect</i> option, this clock is always 125 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| rx_clock_enable_source_o <sup>2</sup> | Out | 1     | Receive Clock Enable Source – This signal is similar to the tx_clock_enable_source_o described above, except that it is used for the receive data path. Note that this signal is only present when the IP core is generated using the <i>TSMAC Easy Connect</i> (G)MII option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| rx_clock_enable_sink_i <sup>2</sup>   | In  | 1     | Receive Clock Enable Sink – This signal is only present when the IP core is generated using the <i>TSMAC Easy Connect</i> (G)MII option. This signal is used in combination with the receive 125 MHz clock to regulate the flow of receive (G)MII data. When the clock enable is high and the receive clock edge rises, (G)MII data is launched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rst_n_i                               | In  | 1     | Reset – Active low global reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| cdr_refclk_i                          | In  | 1     | CDR Reference Clock – 125 MHz user-provided CDR reference clock input.  Note that this signal is only available for non-LAV-AT devices and if <i>Enable Port: CDR Reference clock</i> is enabled. This input clock should be coming from the device's Generic PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| clk_125m_pll_i                        | In  | 1     | 125 MHz PLL Clock – 125 MHz clock input. Note that this signal is only available if <i>Use External PLL</i> is enabled in GUI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| clk_625m_pll_i                        | In  | 1     | 625 MHz PLL Clock – 625 MHz clock input. Note that this signal is only available if <i>Use External PLL</i> is enabled in GUI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| clk_625m_90_pll_i                     | In  | 1     | 90-degree Phase Shift 625 MHz PLL Clock – 625 MHz clock input with 90-degree phase shift. Note that this signal is only available if <i>Use External PLL</i> is enabled in GUI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| pll_refclk_i                          | In  | 1     | PLL Reference Clock – 125 MHz clock input. Data is sampled on the rising edge of this clock. Note that this signal is only available if <i>Use External PLL</i> is disabled in GUI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| clk_125m_pll_o                        | Out | 1     | 125 MHz PLL primary output clock — Note that this signal is only available if<br>Enable Port: CDR Reference clock is enabled in GUI or if Use External PLL is<br>disabled in GUI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| usr_clk_o                             | Out | 1     | User Clock – 125 MHz clock from ECLKDIV output. Note that this signal is only present when the IP core is generated using the <i>TSMAC Easy Connect (G)MII</i> option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Port Name                     | 1/0 | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_gddr_o                    | Out | 1     | DDR Clock – assumes an LVDS buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| lmmi_clk_i                    | In  | 1     | LMMI clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| mdc_i                         | In  | 1     | Management Data Clock – Clock source for the serial management interface. The IEEE 802.3 specification (clause 22) dictates that the maximum frequency for this clock is 2.5 MHz. Note that this signal is only present when the IP core Register Access is in <i>MDIO</i> option.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GMII                          |     | •     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| tx_d_i                        | In  | 8     | Transmit Data – Incoming (G)MII data. Note that this port's behavior varies depending on the (G)MII option used when generating the IP core. For <i>Classic</i> mode, when the (G)MII data rate is 1 Gbps, all 8 bits of tx_d_i are valid. However, for 100 Mbps and 10 Mbps, only bits 3:0 of tx_d_i are valid. For the <i>TSMAC Easy Connect</i> mode all 8 bits of tx_d_i are valid for all (G)MII data rates (1 Gbps, 100 Mbps, 10 Mbps).                                                                                                                                                                                                                                                                                            |

| tx_en_i                       | In  | 1     | Transmit Enable – Active high signal; asserts when incoming data is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tx_er_i                       | In  | 1     | Transmit Error – Active high signal used to denote transmission errors and carrier extension on incoming (G)MII data port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| rx_d_o                        | Out | 8     | Receive Data – Outgoing (G)MII data. Note that this port's behavior varies depending on the (G)MII option used when generating the IP core. For <i>Classic</i> mode, when the (G)MII data rate is 1Gbps, all 8 bits of rx_d_o are valid. However, for 100 Mbps and 10 Mbps, only bits 3:0 of rx_d_o is valid. For the <i>TSMAC Easy Connect</i> mode all 8 bits of rx_d_o is valid for all (G)MII data rates (1Gbps, 100 Mbps, 10 Mbps).                                                                                                                                                                                                                                                                                                 |

| rx_dv_o                       | Out | 1     | Receive Data Valid – Active high signal, asserts when outgoing data is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| rx_er_o                       | Out | 1     | Receive Error – Active high signal used to denote transmission errors and carrier extension on outgoing (G)MII data port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| col_o                         | Out | 1     | Collision Detect – Active high signal, asserts when tx_en_i and rx_dv_o is active at the same time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| crs o                         | Out | 1     | Carrier Sense Detect – Active high signal, asserts when rx_dv_o is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Management                    |     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| mr_adv_ability_i <sup>3</sup> | In  | 16    | Advertised Ability – Configuration status transmitted by PCS during autonegotiation process. This signal must not change during autonegotiation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| mr_an_enable_i <sup>3</sup>   | In  | 1     | Auto-Negotiation Enable – Active high signal that enables auto-negotiation state machine to function. This signal must not change during auto-negotiation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| mr_main_reset_i <sup>3</sup>  | In  | 1     | Main Reset – Active high signal that forces all PCS state machines to reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| mr_restart_an_i <sup>3</sup>  | In  | 1     | Auto-Negotiation Restart – Active high signal that forces auto-negotiation process to restart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| mr_an_complete_o              | Out | 1     | Auto-Negotiation Complete – Active high signal that indicates that the auto-negotiation process is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| mr_lp_adv_ability_o           | Out | 16    | Link Partner Advertised Ability – Configuration status received from partner PCS entity during the auto-negotiation process. The bit definitions are the same as described above for the mr_adv_ability_i port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| mr_page_rx_o                  | Out | 1     | Auto-Negotiation Page Received – Active high signal that asserts while the auto-negotiation state machine is in the <i>Complete_Acknowledge</i> state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| force_isolate_i <sup>3</sup>  | In  | 1     | Force PCS Isolate — Active high signal that isolates the PCS. When asserted, the RX direction forces the (G)MII port to all zeros, regardless of the condition of the incoming 1.25 Gbps serial data stream. In the TX direction, the condition of the incoming (G)MII port is ignored. The TX PCS behaves as though the (G)MII TX input port was forced to all zeros. Note, however, that the isolate function does not produce any electrical isolation — such as tristating of the (G)MII RX outputs of the IP core. When the signal is de-asserted (low), the PCS isolation functions are deactivated. The use of this signal is optional. If the user chooses not to use the isolate function, then this signal should be tied low. |

| force_loopback_i <sup>3</sup> | In  | 1     | Force PCS Loopback – Active high signal that activates the PCS loopback function. When asserted, the 10-bit code-group output of the transmit state machine is looped back to the 10-bit code-group input of the receive state machine. When de-asserted, the loopback function is deactivated.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Port Name                   | I/O        | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             |            |       | The use of this signal is optional. If the user chooses not to use the loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                             |            |       | function, then this signal should be tied low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| force_unidir_i <sup>3</sup> | In         | 1     | Force PCS Unidirectional Mode — Active high signal that activates the PCS unidirectional mode. When asserted, the transmit state machine path between the TX (G)MII input and the TX 10-bit code-group output will remain operational, regardless of what happens on the RX data path. (Normally RX loss of sync, invalid code-group reception, auto-negotiation restarts can force the transmit state machine to temporarily ignore inputs from the TX (G)MII port).                                                                                                           |

|                             |            |       | When de-asserted, the unidirectional mode is deactivated.  The use of this signal is optional. If the user chooses not to use the unidirectional function, then this signal should be tied low.                                                                                                                                                                                                                                                                                                                                                                                 |

| an_link_ok_o                | Out        | 1     | Auto-Negotiation Link Status OK – Active high signal that indicates that the link is ok. The signal is driven by the auto-negotiation state machine. When auto-negotiation is enabled, the signal asserts when the state machine is in the LINK_OK state. If auto-negotiation is disabled, the signal asserts when the state machine is in the AN_DISABLE_LINK_OK state (see IEEE 802.3 figure 37-6).  This signal is intended to be used to produce the <i>Link Status</i> signal as required by IEEE 802.3, Status Register 1, Bit D2 (see IEEE 802.3 paragraph 22.2.4.2.13). |

| Serial Interface            | _          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ser tx o                    | Out        | 1     | Serial Transmit Data – DDR data. Assumes an LVDS buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ser_rx_i                    | In         | 1     | Serial Receive Data – DDR data. Assumes an LVDS buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MDIO                        |            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| mdio_io                     | In/<br>Out | 1     | Management Data Input/Output – Bi-directional signal used to read/write management registers. Note that this signal is only present when the IP core Register Access is in <i>MDIO</i> option.                                                                                                                                                                                                                                                                                                                                                                                  |

| port_id_i                   | In         | 5     | Port Identification Address – Used to define the binary address of this management node. The value used here corresponds to the PHY-ADD portion of the management frame format (specified in IEEE 802.3, clause 22). Note that this signal is only present when the IP core Register Access is in <i>MDIO</i> option.                                                                                                                                                                                                                                                           |

| LMMI                        |            |       | 1 55.13.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| lmmi resetn i               | In         | 1     | LMMI active low reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Immi request i              | In         | 1     | Start transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| lmmi_wr_rdn_i               | In         | 1     | Write = 1'b1, Read = 1'b0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| lmmi_offset_i               | In         | 6     | Register offset, starting at offset 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| lmmi wdata i                | In         | 16    | Output data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| lmmi_rdata_o                | Out        | 16    | Input data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| lmmi_rdata_valid_o          | Out        | 1     | Read transaction is complete and Immi_rdata_o contains valid data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| lmmi_ready_o                | Out        | 1     | IP is ready to receive a new transaction. This is always asserted (tied to 1'b1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Miscellaneous               |            |       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| sgmii_mode_i                | In         | 1     | SGMII Mode – Controls the behavior of the auto-negotiation process when the core is operating in SGMII mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| gbe_mode_i                  | In         | 1     | 0 = operates as MAC-side entity, 1 = operates as PHY-side entity.  Gigabit Ethernet Mode – Controls the core's PCS function.  0 = operates as SGMII PCS, 1 = operates as Gigabit Ethernet PCS (1000BaseX)                                                                                                                                                                                                                                                                                                                                                                       |

| operational_rate_i          | In         | 2     | Operational Rate – When the core operates in SGMII PCS mode, this port controls the regulation rate of the rate adaptation circuit blocks as follows: 10 = 1G bps Rate 01 = 100 Mbps Rate 00 = 10 Mbps Rate Note in Gigabit Ethernet PCS mode, the rate adaptation blocks always operate at the 1Gbps rate, regardless of the settings on the operational_rate_i control pins.                                                                                                                                                                                                  |

| debug_link_timer_short_i    | In         | 1     | Debug Link Timer Mode – Active high signal that forces the auto-negotiation link timer to run much faster than normal. This mode is provided for debug purposes (e.g., allowing simulations to run through the auto-negotiation                                                                                                                                                                                                                                                                                                                                                 |

© 2019-2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Port Name  | 1/0 | Width | Description                                                                                                                |

|------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------|

|            |     |       | process much faster than normal). This signal must not change during autonegotiation.                                      |

| pll_lock_i | In  | 1     | PLL Lock – External PLL lock signal. Note that this signal is only available if <i>Use External PLL</i> is enabled in GUI. |

#### Notes:

- 1. Connect tx\_clock\_enable\_sink\_i to tx\_clock\_enable\_source\_o. Relationships between TX-side signals are shown in Figure 2.3.

- 2. Connect rx\_clock\_enable\_sink\_i to rx\_clock\_enable\_source\_o. Relationships between RX-side signals are shown in Figure 2.4.

# 2.3. Attribute Summary

The configurable attributes of the SGMII IP Core are shown in Table 2.2 and are described in Table 2.3. The attributes can be configured through the IP Catalog's Module/IP wizard of the Lattice Radiant software.

**Table 2.2. Attributes Table**

| Attribute                                       | Selectable Values     | Default   | Dependency on Other Attributes                    |  |  |  |

|-------------------------------------------------|-----------------------|-----------|---------------------------------------------------|--|--|--|

| General                                         |                       |           |                                                   |  |  |  |

| (G)MII Interface                                | Classic, TSMAC        | Classic   | _                                                 |  |  |  |

| CTC Mode                                        | Static, Dynamic, None | Dynamic   | _                                                 |  |  |  |

| Static Low FIFO Threshold                       | 3–1010                | 16        | Editable when CTC Mode == Static                  |  |  |  |

| Static High FIFO Threshold                      | 13–1020               | 32        | Editable when CTC Mode == Static                  |  |  |  |

| Optional Ports                                  |                       |           |                                                   |  |  |  |

| Use External PLL (remove internal PLL instance) | Checked, Unchecked    | Unchecked | _                                                 |  |  |  |

| Enable Port: CDR Reference clock (input)        | Checked, Unchecked    | Unchecked | This option only available for non-LAV-AT devices |  |  |  |

| SGMII Core Register Access                      | LMMI, MDIO            | MDIO      | _                                                 |  |  |  |

Table 2.3. Attributes Descriptions

| Attribute                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (G)MII Interface                                | This attribute affects the behavior and implementation of the (G)MII port. In <i>Classic</i> mode, the (G)MII data port is 8 bits wide. All 8 bits are used for 1Gbps operation. Only the lower 4 bits are used for 100Mbps and 10 Mbps operation. A separate MII clock is used to synchronize the (G)MII data. The MII clock frequency varies with the (G)MII data rate: 125 MHz for 1 Gbps, 25 MHz for 100 Mbps, 2.5 MHz for 10 Mbps. For the <i>TSMAC Easy Connect</i> mode, the (G)MII data port is 8 bits wide; and all 8 bits are used, regardless of the (G)MII data rate. A single 125 MHz clock is used to synchronize (G)MII data; and a clock enable is used to regulate the (G)MII data rate.          |

| CTC Mode                                        | This attribute controls the behavior of the CTC block. In dynamic mode, the CTC FIFO thresholds are automatically changed, based upon the current operational rate of the rate adaptation blocks. Optimal thresholds are internally chosen for the three data rates (1Gbps, 100 Mbps, 10 Mbps). In static mode, the user manually chooses the CTC FIFO thresholds, and these thresholds remain fixed. This mode is used when IP is expected to operate at only data rate (either 1 Gbps, or 100 Mbps, or 10 Mbps). In <i>None</i> mode, the CTC function is replaced by a shallow FIFO that facilitates clock domain crossing between the recovered SERDES clock and the local IP core receive-side 125 MHz clock. |

| Static Low FIFO Threshold                       | When Static CTC mode is chosen, this attribute specifies FIFO low (almost empty) threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Static High FIFO Threshold                      | When Static CTC mode is chosen, this attribute specifies FIFO high (almost full) threshold. This attribute must be higher than the Static Low FIFO Threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Optional Ports                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Use External PLL (remove internal PLL instance) | By default, there is a PLL instance inside the IP that provides clock to the CDR and GDDR block. This option allows the user to remove the internal PLL instance in the IP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

© 2019-2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Attribute                                   | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | This option is useful if the user intends to use some ports of the PLL which will not be possible if it is inside the IP. User applications with multiple SGMII instance may prefer to have a common PLL instead of per IP instance.  For some device like LFMXO5, the reference clock of CDR blocks is tied to a common PLL so this option is needed when implementing with multiple SGMII instance.    |

| Enable Port: CDR Reference clock<br>(input) | This is related to the option above. When enabled, the internal CDR reference clock input is provided as IP port.  For LFMXO5, this should always be enabled regardless of the <i>Use External PLL</i> setting.  CDR and DDR cannot share PLL clocks so user is expected to instantiate a separate PLL in the design. Note that CDR reference clock can only come from CLKOP of the PLL.                 |

| SGMII Core Register Access                  | This attribute controls register access in the SGMII core. In MDIO mode, SGMII core registers (Control, Status, Advertised Ability, Link Partner, Auto Negotiation Expansion, Extended Status, Configuration Source Control) are accessible to MDIO, but PCS registers, Interrupt registers and CDR registers are only accessible through LMMI. In LMMI mode, all registers are accessible through LMMI. |

# 2.4. Register Description

This section provides detailed descriptions of SGMII data registers. Note that registers that are not available to users are highlighted in gray.

The register address map, shown in Table 2.4, specifies the available IP Core registers.

Table 2.4. Register Address Map

| Offset           | Register Name                         | Description                                                                                                                                                                                                             |

|------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x000            | Control Register                      | These are five of the management registers specified in IEEE 802.3,                                                                                                                                                     |

| 0x001            | Status Register                       | Clause 37 – Control, Status, Auto Negotiation Advertisement, Link                                                                                                                                                       |

| 0x004            | Advertised Ability                    | Partner Ability, Auto Negotiation Expansion, and Extended Status. The                                                                                                                                                   |

| 0x005            | Link Partner Ability                  | register set is accessible through LMMI or MDIO interface.                                                                                                                                                              |

| 0x006            | Auto Negotiation Expansion Register   |                                                                                                                                                                                                                         |