#### Features:

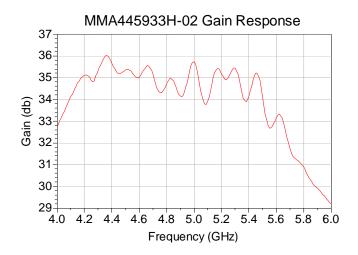

- 30 dB Gain

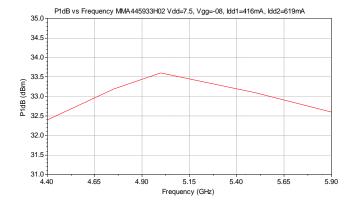

- 33 dBm P-1dB

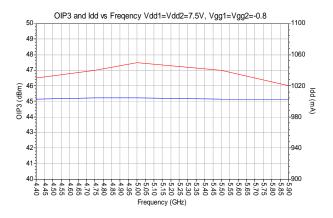

- OIP3 45 dBm

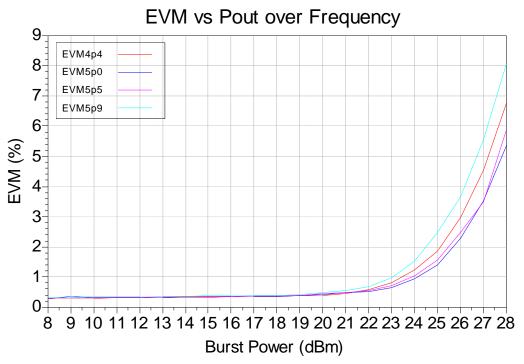

- 26.0 dBm Linear Pout @ 2.5% EVM (802.11 64QAM)

- Fully Matched Input and Output for Easy Cascade

- Internal Bias Tee

- Surface Mount Package

- MTTF > 100 years @ 85°C ambient temperature

#### **Description:**

The MMA-445933H-02 is a power amplifier with the State-of-the-Art linear power-added-efficiency between 4.4 GHz and 5.9 GHz frequency band. Based on advanced robust HFET device technology, the linearity of this power amplifier is 26 dBm linear power at 2.0% EVM and achieves an ACPR better than -38 dBc. The modulation test pattern is 802.16x 64QAM. This linear power amplifier also has high gain. Ideal applications include the driver and the output power stage of WiMax and WLAN infrastructures and access points. It also can be used for PTP (Point-To-Point) radio applications for this band.

## **Typical RF Performance**: Vdd1= 7.5V, Vdd2= 7.5V, Vgg1= -0.8V, Vgg2= -0.8V, Idq1=410mA Idq2=622 mA, Ta=25 °C, Z0=50 ohm

| •                                 |       |              |

|-----------------------------------|-------|--------------|

| Parameter                         | Units | Typical Data |

| Frequency Range                   | MHz   | 4400-5900    |

| Gain (Typ / Min)                  | dB    | 29 / 33      |

| Gain Flatness (Typ / Max)         | +/-dB | 2.5 / 4.5    |

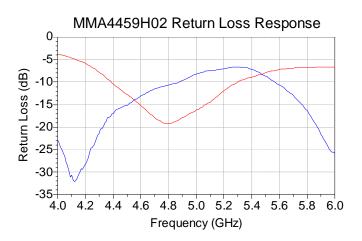

| Input Return Loss                 | dB    | 10           |

| Output Return Loss                | dB    | 7            |

| Output P1dB                       | dBm   | 33           |

| OIP3                              | dBm   | 45           |

| Pout @ 2.5% EVM                   | dBm   | 26.0         |

| Operating Current Range           | mA    | 1050         |

| Thermal Resistance (Driver Stage) | °C /W | 20           |

| Thermal Resistance (Output Stage) | °C /W | 16           |

# MMA-445933H-02 4.4 - 5.9 GHz 2W High Efficiency Linear Power Amplifier

## **Typical RF Performance:** *Vdd1=7.5V,Vdd2=7.5V, Vgg1=-0.8, Vgg2=-0.8V, Idq1=410mA*, *Idq2=620mA*, *Z0=50* ohm, *Ta=25* ℃

#### Maximum Ratings: (Ta= 25 ℃)\*

| SYMBOL      | PARAMETERS                        | UNITS | ABSOLUTE MAXIMUM |

|-------------|-----------------------------------|-------|------------------|

| Vdd1        | Drain-Source Voltage Driver Stage | V     | 10               |

| Vdd2        | Drain-Source Voltage Output Stage | V     | 10               |

| Vgg1        | Gate-Source Voltage Driver Stage  | V     | -5               |

| Vgg2        | Gate-Source Voltage Output Stage  | V     | -5               |

| ldq1        | Drain Current Driver Stage        | mA    | 500              |

| ldq2        | Drain Current Output Stage        | mA    | 750              |

| lg1 and lg2 | Gate Current                      | mA    | 10               |

| lp          | Pinch-Off Current                 | mA    | 10               |

| Pdiss       | DC Power Dissipation              | W     | 9.0              |

| Pin max     | RF Input Power                    | dBm   | +10              |

| Toper       | Operating Temperature             | °C    | -40 to +85       |

| Tch         | Channel Temperature               | °C    | 175              |

| Tstg        | Storage Temperature               | °C    | -55 to 150       |

<sup>\*</sup>Operation of this device above any one of these parameters may cause permanent damage.

## Typical Scattering Parammeters :Vdd1=7.5V,Vdd2=7.5V,Vgg1=-0.8V,Vgg2=-0.8V,Idq1=410mA,Idq2=620mA,Z0=50 ohm, $Ta=25^{\circ}$

#### S-parameeters Vd1=Vdd2 =7.5, Vgg1=Vgg2=-0.8, ldd1=416mA, ldd2=620mA

| freq    | magS11 | AngS11   | magS21 | AngS21   | magS12   | AngS12   | magS22 | AngS22  |

|---------|--------|----------|--------|----------|----------|----------|--------|---------|

| 4.000 G | 0.645  | 32.285   | 43.519 | -99.628  | 0.001    | 97.671   | 0.072  | 22.256  |

| 4.100 G | 0.583  | 19.241   | 50.770 | -128.986 | 0.001    | 103.298  | 0.029  | 58.433  |

| 4.200 G | 0.507  | 3.416    | 56.887 | -160.542 | 0.001    | 104.699  | 0.039  | 136.794 |

| 4.300 G | 0.405  | -13.491  | 58.229 | 171.005  | 0.001    | 99.811   | 0.085  | 155.711 |

| 4.400 G | 0.303  | -28.862  | 60.835 | 137.356  | 0.001    | 96.209   | 0.141  | 147.883 |

| 4.500 G | 0.230  | -43.280  | 58.592 | 113.084  | 0.001    | 99.810   | 0.175  | 141.579 |

| 4.600 G | 0.174  | -60.629  | 56.340 | 89.105   | 0.001    | 97.310   | 0.221  | 137.483 |

| 4.700 G | 0.126  | -77.940  | 57.163 | 60.090   | 0.001    | 86.109   | 0.265  | 128.530 |

| 4.800 G | 0.109  | -97.370  | 54.402 | 43.453   | 0.001    | 94.205   | 0.291  | 122.688 |

| 4.900 G | 0.127  | -120.196 | 51.026 | 18.963   | 0.001    | 128.273  | 0.326  | 119.347 |

| 5.000 G | 0.154  | -141.350 | 61.098 | -5.354   | 0.001    | 117.399  | 0.386  | 111.612 |

| 5.100 G | 0.189  | -153.388 | 49.493 | -24.139  | 2.849E-4 | 158.159  | 0.423  | 101.495 |

| 5.200 G | 0.253  | -162.215 | 57.434 | -52.760  | 0.001    | -171.236 | 0.443  | 91.180  |

| 5.300 G | 0.316  | -175.950 | 59.113 | -79.554  | 0.001    | -178.476 | 0.463  | 77.581  |

| 5.400 G | 0.357  | 169.576  | 50.821 | -99.637  | 0.001    | 163.283  | 0.437  | 61.712  |

| 5.500 G | 0.399  | 158.603  | 50.854 | -137.348 | 0.002    | 176.446  | 0.366  | 48.775  |

| 5.600 G | 0.435  | 147.247  | 45.402 | -151.993 | 0.002    | 169.971  | 0.294  | 37.350  |

| 5.700 G | 0.451  | 137.700  | 38.623 | 177.226  | 0.002    | 168.668  | 0.224  | 29.044  |

| 5.800 G | 0.458  | 131.897  | 35.013 | 157.753  | 0.002    | 169.718  | 0.152  | 25.486  |

| 5.900 G | 0.462  | 128.232  | 31.307 | 137.326  | 0.002    | 162.603  | 0.084  | 29.234  |

| 6.000 G | 0.465  | 123.778  | 28.815 | 115.352  | 0.003    | 170.218  | 0.051  | 72.184  |

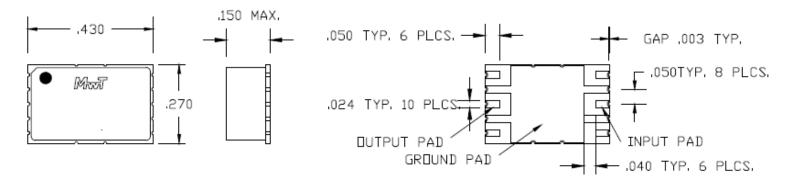

#### **Mechanical Information:**

#### **Package Outline**

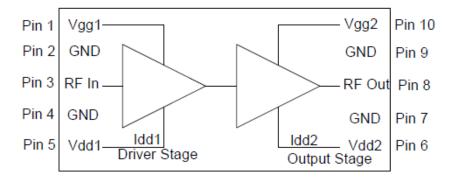

| Pin Designation (Top View) |             |            |             |  |  |

|----------------------------|-------------|------------|-------------|--|--|

| Pin Number                 | Signal Name | Pin Number | Signal Name |  |  |

| 1 Dot Top Left             | Vgg1        | 10         | Vgg2        |  |  |

| 2                          | GND         | 9          | GND         |  |  |

| 3                          | RF In       | 8          | RF Out      |  |  |

| 4                          | GND         | 7          | GND         |  |  |

| 5                          | Vdd1        | 6          | Vdd2        |  |  |

#### All dimensions are in inches

**Figure 1 Functional Diagram**

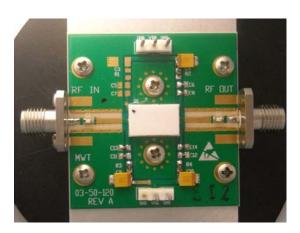

Figure 1 Evaluation board

Figure 2 Hole Layout

#### **Application Note**

The evaluation board, shown in Figure 1, is fabricated with Rogers's 4003 material, 20 mil thick, 2 oz copper weight and includes four DC input connections and two RF lines. The MMA-445933H-02 shown in the center of board is a 2 watt high gain and high linearity amplifier. The MMA-445933H-02 is a 3 stage amplifier assembly die attach to the modified '02' package which includes four bias entries and two RF connections. The bias tees are built-in to the package. Small value bypassing capacitors are included with assembly. Proper bypassing is still required on the DC lines. The amplifier operates over a temperature range of approximately 85°C.

The PCB requires via holes with a diameter of 20 mils placed uniformly over the center pad for thermal relief and RF ground as shown in Figure 2. The via holes can be back filled with conductive epoxy for best thermal performance. The choice of capacitor bypassing near the amplifier should have a short circuit resonance at the frequency of operation. A small capacitor 3.9pf 0603 from AVX has a series resonance at 5.5 GHz and will make a good choice for the first bypass capacitor.

Followed up with larger value capacitors, 100pf or 1000pf and 2.2uF can be used to maintain voltage stability under peak current conditions. The DC ground via holes should be laid out to minimized inductive returns associated with ground loops. Use of stitch ground via holes can help control the return current and also maintain ground continuity between the top and bottom ground layers. Two mounting holes are used near the PA assembly to secure the board to the chassis; this also minimizes ground current loops and improves thermal conductivity in the absence of sweat soldering the board to the chassis. The internal bias tees inside the PA are quarter-wave stubs at the gate and drain inputs. A 56 ohm resistor is inserted in series to the gate increasing the effective impedance seen from the Vgs power supply and reducing the risk of video oscillations. DC blocks are included with assembly; two zero ohm resistors are used at the input and output 50 ohms traces. The MMA-445933H-02 has a noise figure

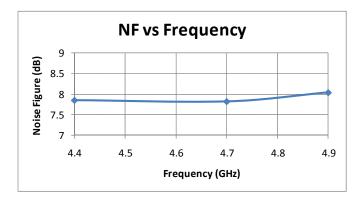

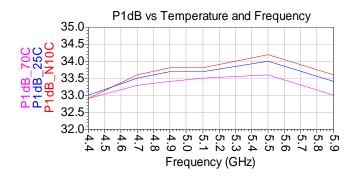

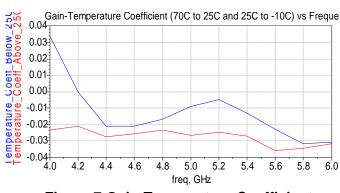

less than 9.0 dB. A plot of noise figure versus frequency at Idq is shown in Figure 3. The amplifier behaves like a class 'A' amplifier. At small signal levels the amplifier operates at Idq. A plot of P1dB versus frequency shown in Figure 4 is plotted from 4.4 to 5.9 GHz. The drain current Idd1 and Idd2 increases over a range of 1050 mA to 1100 mA from Idq = 1020 mA. This bias condition for this amplifier is class A. The gain versus temperature has a negative slope of -0.07 dB/°C. Other class operations can be set by adjusting the gate control voltage(s). Such operations as class B is doable by backing off the PA stage controlled by Vgg2 control voltage. The maximum input drive level is 17 dBm.

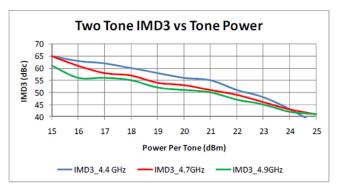

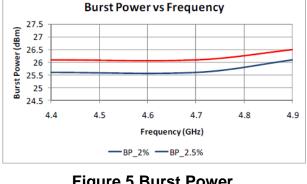

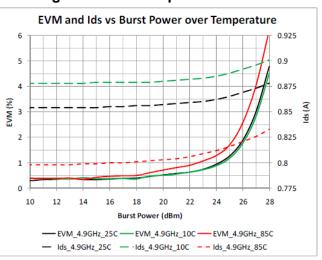

The two tone linearity shown in Figure 4 is swept across a power range from 15 to 25 dBm per tone at the output of the amplifier from 4.4 to 4.9 GHz. At 22 dBm per tone the IMD3 is 50 dBc and OIP3 is 47 dBm. The Burst power shown in Figure 5 is measured across the frequency range from 4.4 to 4.9 GHz at error vector magnitudes equal to 2% and 2.5%. The modulation is 802.16x and each frame cycle has a 10 msec duration and runs continuously. Equalization is enabled when measuring EVM performance. The MMA amplifier bias condition is Vdd1=Vdd2=7.5V and the gate voltage is Vgg1=Vgg2=-0.8V for an Idq=1020 mA.

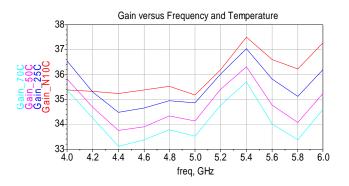

The gain stability over temperature is shown in Figure 6 and 7. The temperature range was taken at 10 C to 85 C deg and varies 3 dB at a fix frequency.

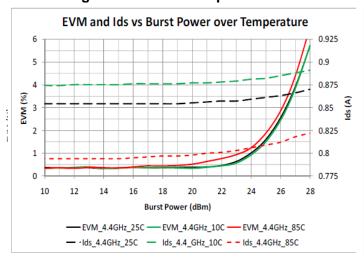

The EVM versus burst power, shown in Figures 8 and 9 is better than 25.5 dBm for an EVM =2% over temperature and is plotted at two spot frequencies points 4.4 GHz and 4.9 GHz from 10C to 85C degrees.

Figure 2 Noise Figure

Figure 3 P1dB and lds

### MMA-445933H-02

4.4 - 5.9 GHz 2W High Efficiency **Linear Power Amplifier**

Figure 4 Two Tone

Figure 5 Burst Power

Figure 6 Gain vs Temperature

**Figure 7 Gain-Temperature Coefficient**

Figure 8 EVM vs Burst Power and Temperature

Figure 9 EVM vs Burst Power and Temperature