Alle Kategorien

-

Integrierte schaltkreise (ICS)

Integrierte schaltkreise (ICS)

- Spezialisierte ICS(35707)

- PMIC-Spannungsregler-besonderer Zweck(1598)

- PMIC-Spannungsregler-lineare Regler(572)

- PMIC-Spannungsregler-linear + Switching(499)

- PMIC-Spannungsregler-linear(27467)

- PMIC-Spannungsregler-DC DC Switching Regulators(20868)

- PMIC-Regler-DC-DC-Switching-Controller(4728)

- PMIC-Spannungs-Referenz(2128)

- PMIC-v/f und f/v-Wandler(47)

- PMIC-Thermal Management(297)

- PMIC-Supervisor(17396)

- PMIC-RMS bis DC-Wandler(555)

- PMIC-Netzteil-Controller, Monitore(723)

- PMIC-Power over Ethernet (PoE) Controller(368)

- PMIC-Power Management-spezialisierte(2708)

- PMIC-Netzschalter, Treiber laden(1429)

- PMIC-PFC (Power Factor Correction)(320)

- PMIC oder Steuerungen, ideale Dioden(290)

- PMIC-Motor-Treiber, Regler(1166)

- PMIC-Beleuchtung, Ballast-Regler(1745)

- PMIC-LED-Treiber(11607)

- PMIC-Laser-Treiber(2349)

- PMIC-Hot-Swap-Controller(2468)

- PMIC-Gate-Treiber(5085)

- PMIC-voll, Half-Bridge-Treiber(364)

- PMIC-Energy Messung(2378)

- PMIC-Display-Treiber(4466)

- PMIC-derzeitige Regulierung/Management(732)

- PMIC-Batterie-Management(3519)

- PMIC-Ladegeräte(46080)

- PMIC-AC DC Konverter, Offline Schalter(21202)

- Memory-Controller(9982)

- Memory-Konfigurations-Proms für FPGAs(7695)

- Speicher-Akkus(130)

- Memory(19527)

- Memory(19527)

- Logic-universelle Bus-Funktionen(31014)

- Logic-Übersetzer, Level-Shifter(755)

- Logik-Specialty Logic(1916)

- Logik-Signal-Schalter, Multiplexer, Decoder(3447)

- Logic-Shift-Register(6058)

- Logic-Parity Generatoren und Checkers(6682)

- Logic-multivibratoren(1274)

- Logik-Latches(1535)

- Logik - Tore und Wechselrichter - Multifunktion, konfigurierbar(4223)

- Logik-Tore und Wechselrichter(5667)

- Logic-Flip Flops(7964)

- Logik-FIFOs Speicher(1236)

- Logik-Zähler, Trennlinien(3350)

- Logik-Vergleichsoperator(5892)

- Logik-Puffer, Treiber, Receiver, Transceiver(6630)

- Linear-Video-Verarbeitung(1075)

- Linear-Vergleichsoperator(2312)

- Linear-analoge Multiplikatoren, Trennwände(1237)

- Linear-Verstärker-Video Amps und Module(3822)

- Linear-Verstärker-Spezial-Zweck(3334)

- Linear - Verstärker - Instrumentierung, OP -Verstärker, Pufferverstärker(11463)

- Linear-Verstärker-Audio(971)

- Interface-Voice Record und Playback(634)

- Schnittstelle - UARTs (Universal Asynchronous Receivers -Sender)(133)

- Schnittstelle-Telecom(47636)

- Interface-spezialisierte(1301)

- Interface-Signal Terminatoren(2351)

- Interface-Signal-Puffer, Repeater, Splitter(1834)

- Interface-Serializer, Deserializer(7226)

- Schnittstellen-Sensor und Detektor-Interfaces(2321)

- Interface-Module(230)

- Interface-Modems-ICS und Module(668)

- Interface-e/a-Expander(2822)

- Interface-Filter-aktiv(1524)

- Interface-Encoder, Decoder, Konverter(11802)

- Interface-Treiber, Receiver, Transceiver(10390)

- Interface-Direct Digital Synthesis (DDS)(3471)

- Interface-Controller(3245)

- Interface-Codecs(583)

- Schnittstelle - Analoge Switches, Multiplexer, Demultiplexer(15690)

- Schnittstelle-analoge Schalter-spezieller Zweck(2961)

- Embedded-System on Chip (SoC)(6429)

- Embedded-PLDs (programmierbare Logik-Vorrichtung)(613)

- Embedded-Mikroprozessoren(5164)

- Embedded-Mikrocontroller-anwendungsspezifische(2091)

- Embedded-Mikrocontroller(59305)

- Eingebettet - Mikrocontroller, Mikroprozessor, FPGA -Module(4518)

- Eingebettet - FPGAs (Feldprogrammiergate -Array) mit Mikrocontrollern(557)

- Embedded-FPGAs (Field Programmable Gate Array)(7189)

- Embedded-DSP (Digital Signal Processors)(4650)

- Eingebettet - CPLDs (komplexe programmierbare Logikgeräte)(4971)

- Datenerfassung-Touch Screen Controller(596)

- Datenerfassung-Digital to Analog Converter (DAC)(5044)

- Datenerfassung-digitale Potentiometer(1879)

- Datenerfassung-analog zu Digital Converters (ADC)(5134)

- Datenerfassung-analoges Frontend (AFE)(227)

- Datenerfassung-MDE/DACs-spezieller Zweck(922)

- Clock/Timing-Uhren in Echtzeit(1372)

- Uhr/Timing - programmierbare Timer und Oszillatoren(1504)

- Clock/Timing-IC-Akkus(492)

- Takt/Timing-Delay Lines(16538)

- Uhr/Timing - Uhrengeneratoren, PLLS, Frequenzsynthesizer(20093)

- Clock/Timing-Clock Puffer, Treiber(3531)

- Clock/Timing-anwendungsspezifische(3433)

- Audio Spezial-Zweck(9718)

-

Diskrete Halbleiter-Produkte

Diskrete Halbleiter-Produkte

- Aktuelle Regulierung - Dioden, Transistoren(775)

- Transistoren-besonderer Zweck(64)

- Transistoren-programmierbare Unijunction(1584)

- Transistoren-jfets(1690)

- Transistoren-IGBTs-Einzel(6032)

- Transistoren-IGBTs-Module(1087)

- Transistoren-IGBTs-Arrays(9)

- Transistoren-FETs, MOSFETs-Einzel(16037)

- Transistoren-FETs, MOSFETs-RF(3251)

- Transistoren-FETs, MOSFETs-Arrays(6376)

- Transistoren-Bipolar (BJT)-einzeln, Pre-biased(4478)

- Transistoren-Bipolar (BJT)-Einzel(12624)

- Transistoren-Bipolar (BJT)-RF(488)

- Transistoren-bipolare (BJT)-Arrays, Pre-biased(6311)

- Transistoren-bipolare (BJT)-Arrays(1394)

- Thyristor-triacs(1128)

- Thyristoren-SCRs-Module(1141)

- Thyristoren-SCRs(2752)

- Thyristoren-diacs, sidacs(164)

- Power Driver Module(4744)

- Dioden-zenerdioden-Einzel(43480)

- Dioden-zenerdioden-Arrays(113195)

- Dioden - variable Kapazität (Varik, Varaktoren)(718)

- Dioden-RF(1765)

- Dioden-Gleichrichter-Einzel(31894)

- Dioden-Gleichrichter-Arrays(8627)

- Dioden-Brücke-Gleichrichter(20238)

-

RF/if und RFID

RF/if und RFID

- SIM -Karten für Abonnenten -Identifikationsmodul (SIM)(41)

- RF -Zirkulatoren und Isolatoren(1721)

- RFID Zubehör(350)

- HF-Zubehör(2025)

- RFID, RF-Zugang, Monitoring-ICS(4567)

- RFID Transponder, Tags(240)

- RFID Lesegeräte(1877)

- RFID Evaluation und Development Kits, Boards(67)

- RFID Evaluation und Development Kits, Boards(67)

- RFID Antennen(696)

- RFI und EMI - Abschirm- und Absorbungsmaterialien(8538)

- HF und EMI-Kontakte, Fingerstock und Dichtungen(4004)

- RF Transmitter(1179)

- RF Transceiver Module(4056)

- RF-Transceiver ICS(1553)

- HF-Schalter(8107)

- RF Shields(4991)

- HF-Receiver(639)

- HF -Empfänger, Sender und Transceiver -Einheiten(3515)

- RF Power Divider/Splitter(4268)

- RF Power Controller ICs(595)

- HF-Modulatoren(3958)

- HF-Mixer(4622)

- RF misc ICS und Module(2738)

- HF-Front-End (LNA + PA)(11681)

- HF Evaluation und Development Kits, Boards(1994)

- HF Evaluation und Development Kits, Boards(1994)

- HF-gerichtete Kupplung(2963)

- RF Diplexer(1406)

- RF-Detektoren(175)

- RF-Demodulatoren(256)

- HF-Antennen(7488)

- HF-Verstärker(17487)

- Balun(706)

- Dämpfungsglieder(3204)

-

Optoelektronik

Optoelektronik

- Optomechanisch(338)

- Leuchten(125)

- Laserdioden, Lasermodule - Laserlieferung, Laserfasern(325)

- Hene Lasersysteme(24)

- Hene Lasersystemzubehör(9)

- Hene Laserköpfe(16)

- Hintergrundbeleuchtung anzeigen(31)

- Laserdioden, Module - Zubehör(36)

- Zubehör(42476)

- Zubehör(42476)

- Xenon-Beleuchtung(549)

- Touchscreen-Overlays(249048)

- Panel Indicators, Pilot Lights(47475)

- Optik-Remote-Phosphor-Lichtquelle(2771)

- Optik-Reflektoren(145)

- Optik-leichte Rohre(3353)

- Optik-Objektive(15458)

- LEDs-Spacer, Unentschieden(433)

- LEDs-Lamp-Ersetzungen(24316)

- LEDs - Leiterplattenindikatoren, Arrays, Lichtstäbe, Balkendiagramme(1922)

- LED-thermische Produkte(6703)

- LED-Beleuchtung(39)

- LED-Beleuchtung-weiß(13461)

- LED-Beleuchtung-Farbe(2210)

- LED-Beleuchtung-Maiskolben, Motoren, Module(9508)

- LED-Anzeige-diskret(10227)

- Laserdioden, Module(1345)

- Lampen-Glühlampen, Neons(338506)

- Lampen-Kälte-Fluoreszenz (KKL) & UV(349)

- Wechselrichter(7962)

- Infrarot, UV, sichtbare Strahler(3759)

- Fiber Optics-Transmitter-Antrieb integriert(3523)

- Fiber Optics-Transmitter-diskrete(2743)

- Fiber Optics-Transceiver Module(22925)

- Fiberoptik-Switches, Multiplexer, Demultiplexer(8234)

- Fiberoptik-Receiver(853)

- Fiberoptik-Dämpfung(394)

- Elektrolumineszenz(24758)

- Display, Monitor-Interface Controller(2642)

- Display-Module-Vakuum-Leuchtstofflampen (VFD)(19327)

- Module anzeigen-LED Dot Matrix und Cluster(17654)

- Display-Module-LED-Zeichen und numerische(2162)

- Display-Module-LCD, OLED, Graphic(3487)

- Display-Module-LCD, OLED-Zeichen und numerische(790)

- Display-Blenden, Objektive(288)

- Adresse, Spezialität(2442)

-

Sensoren, Wandler

Sensoren, Wandler

- Ultraschallempfänger, Sender - Industrial(115)

- Temperatursensoren - Thermostate - Mechanisch - Industrielles(1270)

- Temperatursensoren - Analog und digitaler Ausgang - Industrial(169)

- Näherungssensoren - Industrial(7143)

- Drucksensoren, Wandler - Industrie(1835)

- Optische Sensoren - Photonik - Zähler, Detektoren, SPCM (Einzelphotonzählmodul)(726)

- Optische Sensoren - Kameramodule(776)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module) - Industrie(138)

- Kraftsensoren - Industrial(265)

- Flusssensoren - Industrielles(137)

- Float, Level Sensoren - Industrial(172)

- Encoder - Industrial(2217)

- Farbsensoren - Industrial(20)

- Berührungssensoren(63)

- Messkabel-Zubehör(2553)

- Zubehör(4528)

- Zubehör(4528)

- Ultraschall-Receiver, Transmitter(986)

- Temperatursensoren-Thermostat-Solid State(333)

- Temperatursensoren-Thermostate-mechanisch(4379)

- Temperatursensoren - Thermoelemente, Temperatursonden(1770)

- Temperatursensoren - RTD (Widerstandstemperaturdetektor)(1653)

- Temperatursensoren-PTC-Thermistoren(2026)

- Temperatursensoren-ntc-thermistoren(7932)

- Temperatursensoren-Analog und Digital Output(2963)

- DMS(1886)

- Spezialisierte Sensoren(3142)

- Solarzellen(688)

- Schock-Sensoren(317)

- Sensor-Interface-Junction-Blöcke(2156)

- Sensor-Kabel-Baugruppen(26522)

- Proximity/Belegung Sensoren-fertige Einheiten(902)

- Näherungsschalter(3322)

- Drucksensoren, Wandler(10275)

- Positionssensoren - Winkel, lineare Positionsmessung(3882)

- Optische Sensoren-reflektierende-Logik-Ausgang(1471)

- Optische Sensoren - reflektierend - analoge Ausgang(1258)

- Optische Sensoren-Phototransistoren(1032)

- Optische Sensoren - Photointerrupter - Schlitztyp - Transistorausgang(513)

- Optische Sensoren - Photointerrupter - Schlitztyp - Logikausgabe(559)

- Optische Sensoren-Lichtschranke, Industrial(12132)

- Optische Sensoren-Photodioden(3168)

- Optische Sensoren-Foto-Detektoren-Remote Receiver(1350)

- Optische Sensoren-Foto-Detektoren-Logik-Ausgang(339)

- Optische Sensoren-Foto-Detektoren-CDs-Zellen(717)

- Optische Sensoren-Maus(1297)

- Optische Sensoren-Distanz-Messung(1412)

- Optische Sensoren-Ambient Light, IR, UV Sensoren(10243)

- Multifunktions(1418)

- Motion Sensors-Vibration(1680)

- Motion Sensors-Tilt Schalter(159)

- Bewegungsmelder-optisch(347)

- Motion Sensors-Neigungssensoren(102)

- Motion Sensors-Imus (Trägheit-Maßeinheiten)(298)

- Motion Sensors-Kreisel(702)

- Motion Sensors-Beschleunigungsmesser(764)

- Magnete-Sensor abgestimmt(152)

- Magnete-Multi Purpose(1871)

- Magnetische Sensoren-Schalter (Solid State)(1519)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module)(2148)

- Magnetische Sensoren-linear, Kompass (ICS)(698)

- Magnetsensoren - Kompass, Magnetfeld (Module)(178)

- LVDT -Wandler (linearer variabler Differentialtransformator)(1451)

- IrDA Transceiver-Module(77)

- Bildsensor, Kamera(1272)

- Feuchtigkeit-Sensoren(3880)

- Gas-Sensoren(4294)

- Force Sensoren(1023)

- Durchfluss-Sensoren(440)

- Float, Level Sensoren(634)

- Flex-Sensoren(157)

- Encoder(3440)

- Staub-Sensoren(388)

- Aktuelle Wandler(2256)

- Color Sensoren(49)

- Schnittstelle - Sensor, kapazitive Berührung(356)

- Verstärker(2000)

- Verstärker(2000)

-

Anschlüsse, Verbindungen

Anschlüsse, Verbindungen

- Stecker und Behälter(1710)

- USB, DVI, HDMI Stecker-Zubehör(94)

- Klemmen-Zubehör(113)

- Anschlussblöcke-Zubehör-Draht-Beschläge(1061)

- Anschlussblöcke-Zubehör-Marker-Streifen(4696)

- Anschlussblöcke-Zubehör-Jumper(1477)

- Anschlussblöcke-Zubehör(3886)

- Solid State Lighting Steckverbinder-Zubehör(96)

- Buchsen für ICS, Transistoren-Zubehör(71)

- Rechteckige Steckverbinder-Zubehör(2950)

- Rechteckig-Platine-Stecker-Zubehör(1)

- Power Entry Steckverbinder-Zubehör(329)

- Austauschbare Steckverbinder-Zubehör(204)

- Photovoltaik (Solarpanel) Stecker - Zubehör(99)

- Modulare Anschlüsse - Kabelblöcke - Zubehör(22)

- Modulare Steckverbinder-Zubehör(276)

- Memory Steckverbinder-Zubehör(57)

- Keystone-Zubehör(357)

- Heavy Duty Steckverbinder-Zubehör(1081)

- LWL-Steckverbinder - Zubehör(349)

- FFC, FPC (flache flexible) Steckverbinder - Zubehör(8)

- D -Sub, D -förmige Steckverbinder - Zubehör - JackScrews(830)

- D-Sub, d-förmige Steckverbinder-Zubehör(1168)

- Koaxial Verbinder (RF)-Zubehör(1017)

- Rundsteckverbinder-Zubehör(48982)

- Card Edge Steckverbinder-Zubehör(99)

- Blade Type Power Connectors-Zubehör(670)

- Fass-Zubehör(74)

- Banana and Tip Steckverbinder-Zubehör(25)

- Backplane Steckverbinder-Zubehör(693)

- USB, DVI, HDMI Stecker-Adapter(45761)

- USB, DVI, HDMI Stecker(3377)

- USB, DVI, HDMI Stecker(3377)

- Klemmen-Wire to Board Steckverbinder(1604)

- Klemmen-Draht-Steckverbinder(40747)

- Klemmen-Draht-Pin Stecker(12531)

- Terminals-Revolver Steckverbinder(5553)

- Terminals-spezialisierte Steckverbinder(1300)

- Klemmen-Spaten Verbinder(1381)

- Klemmen-Löten/Stecker(2577)

- Klemmen-Verschraubungen(1980)

- Klemmen-Ring Steckverbinder(6682)

- Klemmen-rechteckige Steckverbinder(3878)

- Terminals - Schnellverbindungen, schnelle Trennungsanschlüsse(4695)

- Klemmen-PC PIN, Single Post Connectors(2149)

- Klemmen-PC-Pin-Buchsen, Sockel-Steckverbinder(2222)

- Klemmen-magnetische Draht-Steckverbinder(3357)

- Klemmen-Messer Steckverbinder(3829)

- Klemmen-Gehäuse, Stiefel(1891)

- Klemmen-Folie Steckverbinder(662)

- Klemmen-Barrel, Bullet-Steckverbinder(5430)

- Klemmen-Adapter(713)

- Terminal-Streifen und Revolver-Boards(11368)

- Terminal Junction Systeme(3288)

- Anschlussblöcke-Draht an Bord(19352)

- Terminal Blocks-spezialisierte(2960)

- Terminal Blocks-Power Distribution(499)

- Anschlussblöcke-Panel Mount(522)

- Terminal Blocks-Interface Module(1639)

- Anschlussblöcke-Kopfzeilen, Stecker und Buchsen(148192)

- Anschlussblöcke-DIN-Schiene, Kanal(10920)

- Anschlussblöcke-Kontakte(306247)

- Anschlussblöcke-Barrier Blocks(44736)

- Anschlussblöcke-Adapter(449)

- Solid State Lighting Verbinder-Kontakte(2509)

- Solid State Lighting Steckverbinder(2295)

- Solid State Lighting Steckverbinder(2295)

- Buchsen für ICS, Transistoren-Adapter(765)

- Buchsen für ICS, Transistoren(2223)

- Buchsen für ICS, Transistoren(2223)

- Shunts, Jumper(821)

- Rechteckige Verbinder-Feder geladen(8043)

- Rechteckige Steckverbinder-Gehäuse(28877)

- Rechteckige Verbinder-Kopfzeilen, Spezial-PIN(5397)

- Rechteckige Anschlüsse - Header, Gefäße, weibliche Sockel(23450)

- Rechteckige Verbinder-Kopfzeilen, männliche Pins(138439)

- Rechteckige Anschlüsse - kostenloses Hängen, Panelhalterung(15074)

- Rechteckige Verbinder-Kontakte(5477)

- Rechteckige Anschlüsse - Board in, Direktdraht zum Board(2459)

- Rechteckige Verbinder-Adapter(251)

- Rechteckig - Brett zu Board -Steckern - Header, Behälter, weibliche Sockel(2982)

- Rechteckig - Brett zu Board -Steckern - Header, männliche Stifte(239)

- Rechteckige Anschlüsse - Board -Abstandshalter, Stacker (Board zu Board)(27782)

- Rechteckige Anschlüsse - Arrays, Kantentyp, Mezzanin (Board zu Board)(14186)

- Stromanschluss-Eingänge, Steckdosen, Module(4831)

- Austauschbare Steckverbinder(5229)

- Austauschbare Steckverbinder(5229)

- Photovoltaik- (Solarpanel) Anschlüsse - Kontakte(69363)

- Photovoltaik (Solar Panel) Steckverbinder(365)

- Photovoltaik (Solar Panel) Steckverbinder(365)

- Modulare Steckverbinder-Verdrahtung Blöcke(653)

- Modulare Steckverbinder-Stecker(2164)

- Modulare Steckverbinder-Stecker Gehäuse(3582)

- Modulare Steckverbinder-Buchsen mit magnetischen(4193)

- Modulare Steckverbinder-Buchsen(15464)

- Modulare Steckverbinder-Adapter(503)

- Memory Connectors-PC Cards-Adapter(859)

- Memory Connectors-PC Card Sockets(1904)

- Memory Connectors-Inline Modul Sockets(2493)

- LGH Steckverbinder(1057)

- Keystone-Einsätze(8467)

- Keystone-Frontplatte, Frames(19410)

- Heavy Duty Steckverbinder-Einsätze, Module(213354)

- Schwerlastanschlüsse - Gehäuse, Kapuzen, Basen(449460)

- Heavy Duty Steckverbinder-Frames(16851)

- Heavy Duty Steckverbinder-Kontakte(6325)

- Heavy Duty Steckverbinder-Baugruppen(1730)

- LWL-Steckverbinder-Gehäuse(4852)

- Glasfaser-Steckverbinder - Adapter(2754)

- LWL-Steckverbinder(215502)

- FFC, FPC (flache flexible) Steckverbinder - Gehäuse(30189)

- FFC, FPC (flache flexible) Anschlüsse - Kontakte(114)

- FFC, FPC (flache flexible) Steckverbinder(12920)

- FFC, FPC (flache flexible) Steckverbinder(12920)

- D-Sub, d-förmige Steckverbinder-Terminatoren(640)

- D-Sub, d-förmige Steckverbinder-Gehäuse(12383)

- D-Sub, d-förmige Steckverbinder-Kontakte(1350)

- D-Sub, D-förmige Steckverbinder-Rückenschalen, Kapuzen(3078)

- D-Sub, d-förmige Steckverbinder-Adapter(976)

- D-Sub Steckverbinder(106471)

- D-förmige Steckverbinder-Centronics(6037)

- Kontakte, Frühling geladen und Druck(7921)

- Kontakte-Multi Purpose(16222)

- Kontakte-"Leadframe"(572)

- Koaxial-Steckverbinder (RF)-Terminatoren(1374)

- Koaxial-Steckverbinder (RF)-Kontakte(279)

- Koaxial-Steckverbinder (RF)-Adapter(5909)

- Koaxial-Steckverbinder (RF)(16068)

- Koaxial-Steckverbinder (RF)(16068)

- Rundsteckverbinder-Gehäuse(221760)

- Rundsteckverbinder-Kontakte(3377)

- Rundsteckverbinder-backschalen und Kabel-Klemmen(44820)

- Rundsteckverbinder-Adapter(7708)

- Rundsteckverbinder(771637)

- Rundsteckverbinder(771637)

- Card Edge Steckverbinder-Gehäuse(577)

- Karte Edge Verbinder-edgeboard Verbinder(497865)

- Card Edge Verbinder-Kontakte(527)

- Card Edge Verbinder-Adapter(2752)

- Blade Type Power Steckverbinder-Gehäuse(2290)

- Blade Type Power Connectors-Kontakte(715)

- Blade-Typ-Stecker(2373)

- Blade-Typ-Stecker(2373)

- Zwischen Serien-Adapter(289)

- Barrel-Stromanschluss(399)

- Barrel-Audio-Anschlüsse(10808)

- Barrel-Audio Adapter(54)

- Banana und Tip Steckverbinder-Buchsen, Stecker(2046)

- Banana and Tip Connectors-Binding Posts(3219)

- Banana und Tip Steckverbinder-Adapter(647)

- Backplane Steckverbinder-spezialisiert(33926)

- Backplane Steckverbinder-Gehäuse(47465)

- Backplane Steckverbinder-Hard metrisch, Standard(7596)

- Backplane Steckverbinder-DIN 41612(4684)

- Backplane Steckverbinder-Kontakte(4419)

- Backplane Connectors-ARINC Einsätze(2322)

- Backplane Steckverbinder-ARINC(3305)

-

Widerstände

-

Kondensatoren

Kondensatoren

- Zubehör(50)

- Zubehör(50)

- Trimmer, Variable Kondensatoren(1088)

- Dünne Folien-Kondensatoren(1724)

- Tantal-Kondensatoren(79518)

- Tantal-Polymer-Kondensatoren(2486)

- Silizium-Kondensatoren(225)

- Niob Oxide Kondensatoren(128)

- Mica und PTFE Kondensatoren(908)

- Folien-Kondensatoren(89898)

- Elektrische Doppelschichtkondensatoren (EDLC), Superkondensatoren(1644)

- Keramische Kondensatoren(261123)

- Kondensatoren-Netzwerke, Arrays(740)

- Aluminium-Elektrolytkondensatoren(39501)

- Aluminium-Polymer-Kondensatoren(2396)

-

Transformatoren

Transformatoren

-

Isolatoren

-

Kristalle, Oszillatoren, Resonatoren

-

Switches

Switches

- Verriegelungsschalter(862)

- Emergency-Stop-Schalter (E-Stop)(752)

- Kabelzugschalter(353)

- Accessoires-Caps(1768)

- Zubehör-Stiefel, Dichtungen(106)

- Zubehör(11056)

- Zubehör(11056)

- Toggle-Schalter(18713)

- Rändelrads Schalter(1050)

- Schalter(9157)

- Snap-Aktion, Endschalter begrenzen(14916)

- Slide-Schalter(24680)

- Selector-Schalter(4460)

- Rotary Switches(5818)

- Rocker Schalter(60676)

- Drucktaste-Schalter-Hall-Effekt(3768)

- Drucktaste Schalter(29541)

- Programmierbare Display-Switches(13202)

- Navigations-Schalter, Joystick(14105)

- Magnetische, Reed-Schalter(604)

- Keypad-Schalter(168067)

- Keylock Schalter(1623)

- DIP Schalter(2977)

- Konfigurierbare Switch-Komponenten-Objektiv(1755)

- Konfigurierbare Schalter-Komponenten-Lichtquelle(1239)

- Konfigurierbare Switch-Komponenten-Contact Block(2781)

- Konfigurierbare Switch-Komponenten-Body(17732)

-

Relais

Relais

- Sicherheitsrelais(722)

- Reedrelais(484)

- Hochfrequenz (RF) -Relais(461)

- Schütze (Festkörper)(64)

- Schütze (elektromechanisch)(10945)

- Kfz-Relais(1280)

- Zubehör(2791)

- Zubehör(2791)

- Solid State Relais(3585)

- Signal-Relais, bis zu 2 Ampere(6811)

- Relay-Sockets(869)

- Power Relays, über 2 Ampere(369115)

- E / A-Relaismodule(593)

- I/o-Relay-Module-Input(30134)

- I/o-Relay-Module-Analog(438223)

- I/o-Relay-Modul-Racks(14318)

Sprache auswählen

Aktuelle Sprache

Deutsch

- English

- Deutsch

- Italia

- Français

- 日本語

- 한국의

- русский

- Svenska

- Nederland

- español

- Português

- polski

- Suomi

- Gaeilge

- Slovenská

- Slovenija

- Čeština

- Melayu

- Magyarország

- Hrvatska

- Dansk

- românesc

- Indonesia

- Ελλάδα

- Български език

- Afrikaans

- IsiXhosa

- isiZulu

- lietuvių

- Maori

- Kongeriket

- Монголулс

- O'zbek

- Tiếng Việt

- हिंदी

- اردو

- Kurdî

- Català

- Bosna

- Euskera

- العربية

- فارسی

- Corsa

- Chicheŵa

- עִבְרִית

- Latviešu

- Hausa

- Беларусь

- አማርኛ

- Republika e Shqipërisë

- Eesti Vabariik

- íslenska

- မြန်မာ

- Македонски

- Lëtzebuergesch

- საქართველო

- Cambodia

- Pilipino

- Azərbaycan

- ພາສາລາວ

- বাংলা ভাষার

- پښتو

- malaɡasʲ

- Кыргыз тили

- Ayiti

- Қазақша

- Samoa

- සිංහල

- ภาษาไทย

- Україна

- Kiswahili

- Cрпски

- Galego

- नेपाली

- Sesotho

- Тоҷикӣ

- Türk dili

- ગુજરાતી

- ಕನ್ನಡkannaḍa

- मराठी

Umfassender Leitfaden für Feldeffekttransistoren

Zeit: 2024/06/24

Durchsuchen: 690

Katalog

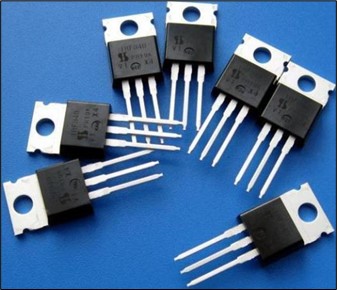

Abbildung 1: Eine Sammlung von Feldeffekttransistoren

FETS in der modernen Elektronik

Feldeffekttransistoren (FETs) sind Schlüsselkomponenten in der modernen Elektronik, die ein elektrisches Feld nutzen, um den Stromfluss zu modulieren.Diese Transistoren sind aufgrund ihrer Fähigkeit bei der effizienten Verwaltung und Verstärkung von Signalen unverzichtbar.Im Kern ihres Betriebs steht die Anwendung der Spannung auf einen Gate -Anschluss, was wiederum die Leitfähigkeit eines Kanals zwischen Quelle und Abflussanschlüssen steuert.Diese Eigenschaft stellt sicher, dass FETs eine hohe Eingangsimpedanz und einen geringen Stromverbrauch aufweisen, was sie für tragbare und batteriebetriebene Geräte außergewöhnlich eignet.Ihre Fähigkeit, als effiziente Schalter oder Verstärker zu fungieren, untermauert ihre weit verbreitete Verwendung in einer Vielzahl elektronischer Anwendungen.

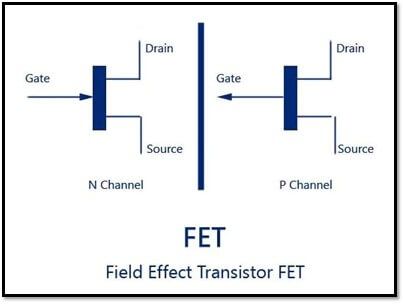

Schlüsselkomponenten des FET

Ein FET besteht aus drei grundlegenden Komponenten: Quelle, Abfluss und Tor.Die Quellanschlüsse dienen als Einstiegspunkt für Strom und liefert die Mehrheit der Ladungsträger, unabhängig davon, ob es sich um Elektronen oder Löcher handelt.Der Abflussanschluss (D) fungiert als Ausgangspunkt, an dem die meisten Ladungsträger den Kanal verlassen.Das Gate -Terminal (G) ist maßgeblich zur Kontrolle der Leitfähigkeit zwischen Quelle und Abfluss beteiligt.Durch Variation der auf das Tor angelegten Spannung wird das elektrische Feld innerhalb des FET verändert, wodurch der Stromfluss zwischen Quelle und Abfluss reguliert wird.Diese Verordnung ermöglicht es dem FET, als präziser Schalter oder Verstärker zu fungieren, wodurch er für verschiedene elektronische Schaltkreise ein wesentlicher Bestandteil ist.

Schlüsselparameter von FETs

Abbildung 2: vereinfachtes Feld Effekttransistorsymbol für den Feld Effekt

Mehrere Schlüsselparameter definieren die Leistung von FETs und beeinflussen ihre Eignung für verschiedene Anwendungen.Transkonduktanz misst, wie effektiv der FET Änderungen der Gate -Spannung in Variationen des Abflussstroms überträgt, wobei eine höhere Transkonduktanz überlegene Leistung hinweist, insbesondere bei Verstärkungsaufgaben.Die Drain-Source-Sättigungsspannung bezeichnet die minimale Spannung, die an den Abflussanschlüssen erforderlich ist, damit der FET den Sättigungsmodus eintritt, wo sie als Verstärker optimal funktioniert.Die Gate -Schwellenspannung ist die kritische Gate -Spannung, die erforderlich ist, um einen leitenden Pfad zwischen Quelle und Abfluss festzulegen, der das Schaltverhalten des FET diktiert.On-Resistenz repräsentiert den Widerstand zwischen Abfluss und Quelle, wenn der FET vollständig eingeschaltet ist.Niedrigere On-Resistenzwerte verbessern die Effizienz und minimieren den Stromverlust, was bei Leistungsanwendungen besonders signifikant ist.

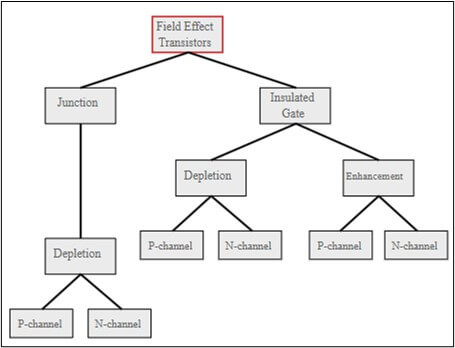

Arten von Feldeffekttransistoren (FETs)

Die vielfältige Landschaft der Feldwirkungstransistoren (FETs) umfasst verschiedene Arten, die spezifischen Betriebsbedürfnissen entsprechen.Ein prominenter Typ ist der Junction Field Effect Transistor (JFET), der einen Halbleiterkanal (entweder N-Typ oder P-Typ) und drei Klemmen umfasst: Gate, Quelle und Abfluss.Das Gate moduliert den Strom über den Kanal und ermöglicht es dem JFET, in zahlreichen elektronischen Schaltungen als zuverlässiger Schalter oder Verstärker zu fungieren.

Ein weiterer bemerkenswerter Typ ist der Transistor (Metal-Oxid-Semiconductor Field Effect Effect) (MOSFET).MOSFETs verfügen über eine Siliziumdioxid -Isolierschicht zwischen dem Gate und dem Kanal, das eine hohe Eingangsimpedanz und einen niedrigen Gate -Strom ermöglicht, wodurch deren Effizienz verbessert wird.MOSFETs werden in den Verbesserungsmodus und den Depletion -Modus eingeteilt, wobei jeweils unterschiedliche Betriebsvorteile angeboten werden.Der Verbesserungsmodus -MOSFETs erfordern eine positive Gate -Spannung, während die MOSFETs des Depletionsmodus standardmäßig leiden und eine negative Gate -Spannung zum Ausschalten erfordern.

Praktische Anwendungen von FETs

Abbildung 3: Arten von Feldeffekttransistoren

Feldeffekttransistoren (FETs) sind aufgrund ihrer hohen Eingangsimpedanz, niedrigen Rauschen und effizienten Schaltfunktionen ein wesentlicher Bestandteil praktischer Anwendungen in verschiedenen Bereichen.In Audiosystemen sorgen FETs sicher, dass die Schallreproduktion mit hoher Quellenstärke durch Minimierung von Rauschen und Verzerrungen eine minimierte Reproduktion von hoher Finderschaft gewährleisten, wodurch sie bei Verstärkern und Mixern unverzichtbar sind.Sie sind auch in RF -Anwendungen von Bedeutung, bei denen ihre Fähigkeit, bei hoher Frequenzen mit minimalem Verlust zu arbeiten, die Signalübertragung und -empfang in Geräten wie Funkgeräten und Mobiltelefonen verbessert.In digitalen Schaltkreisen bilden FETs das Rückgrat von Logik-Toren und -Mikroprozessoren, wodurch ein schnelles Schalten und einen geringen Stromverbrauch für Hochgeschwindigkeits-Computing erforderlich sind.Ihre Rolle bei der Leistungselektronik ist bemerkenswert, wobei Anwendungen in Netzteilen und Motorsteuerungsschaltungen, in denen sie Spannung und Strom effizient regulieren, regulieren.

Arten von JFETs und Voreingenommenheitstechniken

Der Junction Field Effect-Transistor (JFET) dient als grundlegende Komponente in der modernen Elektronik, die als elektronisch gesteuerter Schalter, Verstärker oder Spannungsresistenz verwendet wird.Der JFET ist für seine hohe Eingangsimpedanz und niedrige Rauschmerkmale bekannt und spielt eine bedeutende Rolle in einer Vielzahl von elektronischen Schaltungen.

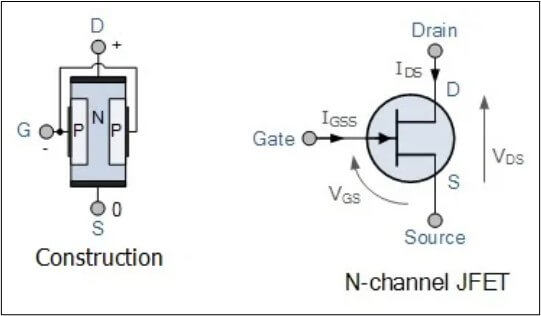

Es gibt zwei Haupttypen von JFETs, die sich durch die Art des in ihren Kanälen verwendeten Halbleitermaterialien auszeichnen.Der erste Typ ist der N-Kanal-JFET, bei dem der Kanal aus N-Typ-Halbleitermaterial besteht und das Tor aus P-Typ-Material besteht.Der zweite Typ ist der P-Kanal-JFET, bei dem der Kanal aus P-Typ-Halbleitermaterial besteht und das Tor aus N-Typ-Material besteht.Diese beiden Arten von JFETs bieten Flexibilität beim Schaltungsdesign und ermöglichen es den Ingenieuren, den entsprechenden Typ basierend auf den spezifischen Anforderungen ihrer elektronischen Anwendungen auszuwählen.

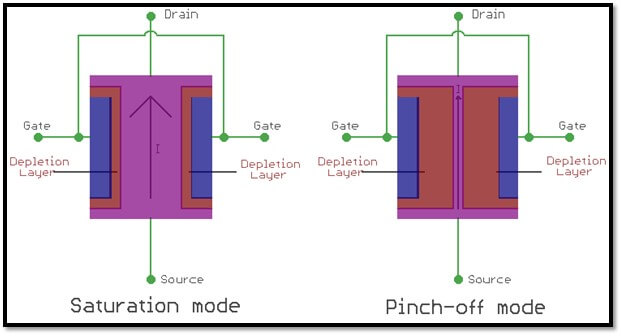

Abbildung 4: Symbol des JFETS -Modus

Pinch-Off ist ein bedeutendes Konzept für den Betrieb von JFETs.Es tritt auf, wenn die Drain-Source-Spannung (V_DS) bis zu dem Punkt erhöht wird, an dem der Spannungsabfall über den Kanal in der Nähe des Abflussende so groß wird, dass sich der Kanal erheblich verengt und den Stromfluss effektiv "einklemmen".In diesem Stadium erstreckt sich der Depletionsregion vom Tor zum Kanal und verengt den Kanal so auf den Punkt, an dem sie weitere Stromerhöhungen einschränkt.In einem N-Kanal-JFET geschieht dies, wenn V_DS ausreichend hoch ist, dass die Gate-Source-Spannung (V_GS) abzüglich des Spannungsabfalls entlang des Kanals der Spannung der Spannung entspricht.Über diesen Punkt hinaus bleibt der Strom (I_D) durch das Gerät unabhängig von weiteren Erhöhungen der V_DS relativ konstant und führt das JFET dazu, in seinen Sättigungsbereich einzugeben.

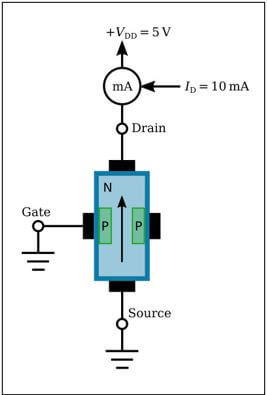

Abbildung 5: Nullbias

Der Sättigungsmodus, auch als aktiver Bereich bezeichnet, ist der Betriebsbereich eines JFET, nachdem ein Prise-Off aufgetreten ist.In diesem Modus verhält sich das JFET als konstantes Stromgerät.Sobald der Kanal eingeklemmt ist, wirkt sich jede weitere Erhöhung der V_DS den Abflussstrom (I_D) nicht wesentlich aus, was relativ konstant bleibt.Dies liegt daran, dass das elektrische Feld in der Nähe des Abflusses stark genug ist, um einen schmalen, aber leitenden Kanal für den Strom mit minimaler Variation aufrechtzuerhalten.In diesem Modus wird der Abflussstrom hauptsächlich von der Gate-Source-Spannung (V_GS) als der Drain-Source-Spannung (V_DS) gesteuert.Der Sättigungsmodus ist für Verstärkungszwecke sehr wichtig, da für einen vorhersehbaren Betrieb ein stetiger Strom erforderlich ist.Bei N-Kanal-JFETs ist das Erreichen und Aufrechterhalten dieses Modus der Schlüssel zu einer effektiven Signalverstärkung und einem konsistenten Transistorverhalten.

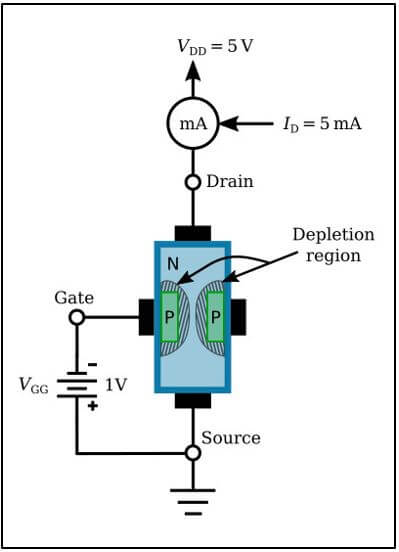

Abbildung 6: Umgekehrte Vorspannung

Stellen Sie sich eine Verkehrsspur auf einer Autobahn vor, um den Betrieb eines JFET weiter zu verstehen.Wenn die Fahrspur klar ist, können sich Fahrzeuge ohne Obstruktion frei bewegen, ähnlich wie Elektronen, die in einem JFET durch einen weit geöffneten Kanal fließen.Denken Sie nun an eine Mautstelle, die seine Barriere anpassen kann, um die Anzahl der Fahrzeuge zu steuern.Wenn die Mautstelle beginnt, seine Barriere zu senken, können jeweils weniger Fahrzeuge vergehen, sobald der Stromfluss in einem JFET abnimmt, wenn sich der Kanal verengt.Wenn zwischen dem Gate und der Quelle keine Spannung aufgetragen wird, ist der Kanal des JFET vollständig geöffnet, sodass die Elektronen wie eine ungehinderte Verkehrsspur ungehindert fließen können.Wenn jedoch eine Rückspannung zwischen dem Tor und der Quelle angewendet wird, wird die P-N-Verbindung umgekehrt voreingenommen.Dies ähnelt der Mautkabine, die ihre Barriere senkt, die Erschöpfungsschicht erhöht und somit den Kanal verengt.Die reduzierte Kanalbreite schränkt den Stromfluss ein, ähnlich wie weniger Fahrzeuge durch die teilweise verringerte Mautkabine gehen können.

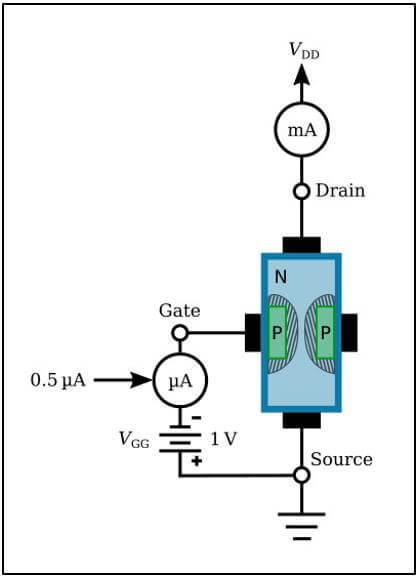

Abbildung 7: Eingangsimpedanz

Wenn die Gate-Source-Spannung hoch genug ist, kann sie den Kanal vollständig abkrusten, ähnlich wie die Mautkabine, die die Fahrspur vollständig blockiert und den gesamten Fahrzeugfluss anhält.Diese Analogie zeigt, wie ein JFET den Stromfluss durch seinen Kanal steuert, indem die Kanalbreite variiert, ähnlich wie eine Mautstelle den Fahrzeugverkehr auf einer Autobahn reguliert.

JFETs (Übergangsfeldtransistoren) sind in einer umgekehrten Konfiguration typischerweise verzerrt, was bedeutet, dass die Gate-Source-Spannung in Bezug auf die Quellspannung negativ ist.Diese umgekehrte Verzerrung ist für den ordnungsgemäßen Betrieb des JFET erforderlich, um eine stabile und vorhersehbare Leistung zu gewährleisten.

N-Kanal-Feldeffekttransistoren

Ein N-Channel-Feldeffekttransistor (FET) ist eine Art Transistor, der die Leitfähigkeit unter Verwendung der auf seinen Gate-Anschluss angewendeten Spannung reguliert.In der Regel aus Silizium, enthält dieser FET drei Klemmen: Quelle, Abfluss und Tor.Der leitende Kanal zwischen Quelle und Abfluss wird durch die Bewegung von Elektronen festgelegt, die die Mehrheit der Ladungsträger in N-Kanal-JFETs sind.Wenn eine positive Spannung auf das Tor relativ zur Quelle angewendet wird, entsteht ein elektrisches Feld, das Elektronen anzieht.Diese Anziehung ermöglicht es den Elektronen, von der Quelle zum Abfluss zu fließen und die Stromleitung zu erleichtern.

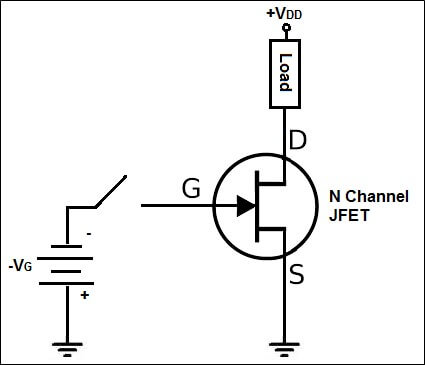

Kontrolle eines N-Kanal-JFET: Aktivierung und Deaktivierung

Abbildung 8: N-Kanal-JFET-Symbol

Um einen N-Kanal-JFET zu aktivieren, wird eine positive Spannung (V_DD) auf den Abflussanschluss angewendet, während das Gate-Terminal bei 0 V hält.Dieses Setup erzeugt ein elektrisches Feld, das Elektronen durch den Drain-Source-Kanal treibt und den Strom fließen lässt.Mit der Gate-Spannung (V_G) bei 0V arbeitet der N-Kanal-JFET in seinem aktiven Bereich und erleichtert den maximalen Stromfluss von Drain zu Quelle.Dies geschieht, weil das Fehlen einer negativen Gate-Spannung den Abbaubereich am Gate-Channel Junction minimal hält und sicherstellt, dass der Kanal für den Elektronenfluss weit geöffnet bleibt.Diese Konfiguration ist für Anwendungen geeignet, bei denen das JFET als Schalter oder Verstärker fungieren muss und einen zuverlässigen Pfad für den Stromfluss bietet.Beispielsweise stellt die Aufrechterhaltung des Tors bei 0V in Verstärkungsschaltungen sicher, dass das JFET die Signale effektiv verstärken kann.

Um einen N-Kanal-JFET zu deaktivieren, wird entweder die positive Vorspannung (V_DD) am Abfluss abgeschnitten, oder eine negative Spannung wird auf den Gate-Anschluss angelegt.Das Entfernen oder erhebliche Reduzieren der Abflussspannung (V_DD) stoppt die Antriebskraft für den Elektronenfluss und schaltet das JFET effektiv aus.Diese Methode ist unkompliziert, bietet jedoch möglicherweise nicht die für einige Anwendungen benötigte Genauigkeit, insbesondere wenn die allmähliche Kontrolle des Stroms erforderlich ist.Durch die Anwendung einer negativen Spannung auf das Tor erhöht sich die umgekehrte Verzerrung an der Gate-Source-Verbindung, erweitert die Verarmungsregion und verengt den leitenden Kanal.Wenn die Gate -Spannung negativer wird, schränkt sie den Kanal weiter ein, bis der Stromfluss auf Null reduziert wird.Diese Methode ermöglicht eine präzise Kontrolle über das JFET, sodass sie für Anwendungen geeignet ist, die eine feine Regulierung des Stroms erfordern.

Konstruktions- und Betriebsprinzip eines N-Kanal-JFET

Die Konstruktion eines N-Channel Junction Field Effect Transistor (JFET) umfasst mehrere Schlüsselelemente, die jeweils zur Funktionalität und Effizienz des Geräts beitragen.Das Fundament des N-Kanal-JFET ist das N-Typ-Halbleiter-Substrat vom Typ N-Typ, das leicht mit Spenderverunreinigungen, typischerweise Phosphor, um den primären leitenden Pfad für Elektronen bildet.Dieses N-Typ-Material wird zur Erstellung eines Kanals benötigt, durch den Elektronen von der Quelle zum Abfluss fließen können, die durch eine angelegte Spannung angetrieben werden.Das leichte Dotieren stellt sicher, dass der Kanal eine angemessene Leitfähigkeit aufweist und gleichzeitig die Kontrolle über den Elektronenfluss über das Tor beibehält.

Abbildung 9: N-Kanal-JFET-Grundstruktur

An jedem Ende des N-Typ-Kanals werden stark dotierte N+ -Regionen erstellt, um die Quellen- (S )- und Drain (D) -klemmen zu bilden.Diese Regionen werden durch einen Diffusions- oder Ionenimplantationsprozess eingeführt, was zu Bereichen mit hoher Konditivität führt, die eine effiziente Elektroneninjektion und Erhebung ermöglichen.Die Quelle ist das Terminal, an dem Elektronen in den Kanal eintreten, während der Abfluss sie verlassen, und durch die Drain-Source-Spannung (V_DS) erleichtert.Diese Anordnung sorgt für niedrige Widerstandspfade an den Eingangs- und Ausgangspunkten und verbessert den Gesamtstromfluss durch das JFET.

Die Gate-Regionen werden durch Diffusion von P-Typ-Material in das N-Typ-Substrat auf beiden Seiten des Kanals gebildet, wodurch P-N-Übergänge zwischen dem Gate und dem N-Typ-Kanal erzeugt werden.Das Tor wird effektiv in zwei symmetrische p-Typ-Regionen aufgeteilt, die den Kanal flankieren, sodass es die Breite und Leitfähigkeit des Kanals steuern kann.Durch die Anwendung einer Gate-Source-Spannung (V_GS) kann die Breite des Verarmungsbereichs an der P-N-Verbindung moduliert werden, was wiederum den Stromfluss zwischen Quelle und Abfluss steuert.Die Gate -Spannung beeinflusst den Kanal, indem sie den Elektronenfluss entweder abbauen oder verbessert und eine präzise Kontrolle über den Betrieb des JFET liefert.

Eine dünne isolierende Schicht aus Siliziumdioxid (SiO₂) wird über den Gate -Regionen gezüchtet und dient dazu, das Tor elektrisch vom Kanal zu isolieren.Diese Isolation stellt sicher, dass das Gate die Leitfähigkeit des Kanals nur durch den elektrischen Feldffekt steuern kann, ohne dass der Gleichstrom zwischen dem Gate und dem Kanal fließt.Diese hohe Eingangsimpedanz ist eines der definierenden Merkmale von JFETs, wodurch sie in verschiedenen elektronischen Anwendungen hocheffizient sind.

Metallkontakte werden dann an den Bereichen Quelle, Abfluss und Gate unter Verwendung von Techniken wie Sputter oder Verdunstung abgelagert, typischerweise unter Verwendung von Aluminium oder anderen geeigneten Metallen.Photolithographische Methoden werden verwendet, um das Metall genau zu prüfen und genaue und zuverlässige elektrische Verbindungen zu gewährleisten.Diese Kontakte liefern die erforderlichen Wege zum Schnittstellen des JFET mit externen Schaltungen und erleichtern den Stromfluss durch Quelle und Abfluss und ermöglichen die Anwendung von Steuerspannungen auf das Gate.

In der symbolischen Darstellung des N-Kanal-JFET wird gezeigt, dass das Tor den Stromfluss zwischen dem Abfluss und der Quelle steuert.Dieses Symbol vermittelt visuell die Beziehung zwischen der Gate-Source-Spannung (V_GS) und dem Drain-Source-Strom (i_ds).Im Betrieb wehrt eine negative Gate-Source-Spannung (für ein N-Kanal-JFET) Elektronen aus dem Kanal ab, wodurch die Breite des Verarmungsbereichs erhöht und damit den Stromfluss durch das Gerät gesteuert wird.

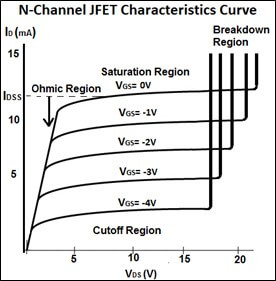

Eigenschaftenkurve eines N-Kanal-JFET

Die Eigenschaftenkurve eines N-Channel Junction Field Effect Transistor (JFET) liefert wertvolle Einblicke in das Verhalten des Geräts unter unterschiedlichen elektrischen Bedingungen.Diese Kurve zeigt die Beziehung zwischen dem Abflussstrom (I_D) und der Drain-Source-Spannung (V_DS) für verschiedene Gate-Source-Spannungen (V_GS).

Abbildung 10: N-Kanal-Eigenschaftenkurve

Die Eigenschaftenkurve für einen N-Kanal-JFET zeigt verschiedene Regionen: die Ohmic-Region, die Sättigungsregion, die Grenzregion und die Aufschlüsselungsregion.Jede Region repräsentiert eine andere Betriebsart für das JFET, das für seine Anwendung in elektronischen Schaltungen von grundlegender Bedeutung ist.

In der ohmischen Region verhält sich das JFET wie ein variabler Widerstand.Der Abflussstrom (I_D) erhöht sich linear mit einer Erhöhung der Abfluss-Source-Spannung (V_DS) für eine bestimmte Gate-Source-Spannung (V_GS).Diese lineare Beziehung wird in Anwendungen verwendet, die einen von der Gate -Spannung gesteuerten variablen Widerstand erfordern.Für praktische Anwendungen ist dieser Bereich in analogen Schaltungen von Vorteil, wenn eine genaue Kontrolle des Widerstands erforderlich ist.Die Steigung der Kurve in diesem Bereich repräsentiert die Transkonduktanz (G_M) des JFET, was auf ihren Gewinn hinweist.

Wenn V_DS weiter zunimmt, tritt das JFET in den Sättigungsbereich ein, in dem I_D relativ konstant und unabhängig von V_Ds wird.Hier fungiert der JFET als konstante Stromquelle, ideal für Verstärkerzwecke.Die Gate-Source-Spannung (V_GS) steuert die Strommenge über das Gerät und sorgt für die Signalverstärkung nützlich.Ingenieure nutzen dieses Merkmal, um stabile und hohe Verstärker zu entwerfen.Der Sättigungsbereich ist durch einen flachen Teil der Kurve gekennzeichnet und zeigt den maximalen Strom, den der JFET für ein gegebenes V_GS durchführen kann.

Wenn die Gate-Source-Spannung (V_GS) ausreichend negativ wird, erzeugt sie eine starke umgekehrte Vorspannung am Gate, wodurch der Depletionsbereich erweitert und schließlich den Kanal abgerissen wird und in den Grenzbereich eintritt.In diesem Bereich ist der Abflussstrom (I_D) vernachlässigbar und der JFET wird effektiv ausgeschaltet.Dieses Merkmal wird in Schaltanwendungen verwendet, bei denen der JFET den Stromfluss vollständig stoppen muss.

Bei höheren Werten von V_DS kann der JFET in den Aufschlüsselungsbereich eingeben, in dem der Abflussstrom aufgrund von Lawinenverschlussen schnell zunimmt.Diese Region wird normalerweise im normalen Betrieb vermieden, da sie das Gerät beschädigen kann.

Die Transkonduktanz (G_M) eines JFET repräsentiert den Gewinn des Transistors und wird durch die Steigung der I_D vs. V_GS -Kurve in den Regionen Ohmic und Sättigung dargestellt.Je höher die Transkonduktanz ist, desto höher ändert sich die Empfindlichkeit gegenüber V_GS, wodurch das JFET am Gate empfindlicher gegenüber kleinen Spannungsänderungen empfindlicher wird.Diese Eigenschaft ist nützlich im Verstärkerdesign, bei dem eine präzise Steuerung des Ausgangsstroms erforderlich ist.Das Betriebsverhalten des JFET in verschiedenen Regionen unterstreicht seine Vielseitigkeit und Anpassungsfähigkeit in einer Vielzahl elektronischer Anwendungen.

Durch den Betrieb eines N-Kanal-JFET werden v_gs sorgfältig ausgewählt, um das Gerät im gewünschten Bereich zu positionieren.Für lineare Anwendungen wird die ohmische Region bevorzugt.Für Verstärkerzwecke ist der Sättigungsbereich optimal.Durch Schaltanwendungen wird häufig die Grenzregion verwendet, um sicherzustellen, dass der JFET vollständig ausgeschaltet ist.Die Auswirkungen von V_GS auf I_D sind signifikant, da unterschiedliche V_GS -Werte den Betriebspunkt des Geräts verschieben.

Bei der Verwendung eines N-Kanal-JFET ist es wichtig, thermische und Spannungsbewertungen zu berücksichtigen, um zu verhindern, dass der Eintritt in den Breakdown-Bereich eintritt.Die Linearität im ohmischen Bereich kann für die analoge Signalverarbeitung ausgenutzt werden, während der konstante Strom im Sättigungsbereich ideal für eine stabile Verstärkung ist.Die Ingenieure müssen sicherstellen, dass die Gate -Spannung genau gesteuert wird, um den gewünschten Betriebsbereich aufrechtzuerhalten, wodurch übermäßige negative V_Gs vermieden werden, die das JFET in Grenzwert oder Aufschlüsselung bringen können.

Unterschiede zwischen P-Kanal-JFETs und N-Kanal-JFETs

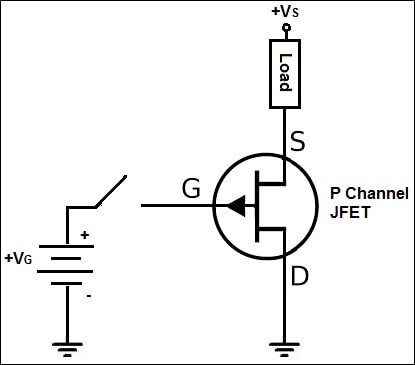

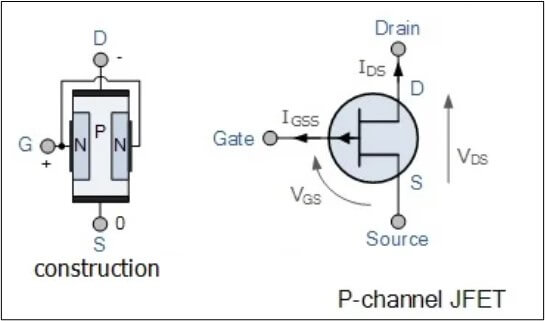

Ein P-Channel Junction Field-Effect Transistor (JFET) funktioniert ähnlich wie sein N-Kanal-Gegenstück, verwendet jedoch Löcher als primäre Ladungsträger anstelle von Elektronen.Beide Typen umfassen drei Klemmen: Quelle, Abfluss und Gate.In einem P-Kanal-JFET erzeugt eine negative Spannung, die relativ zur Quelle an das Tor angewendet wird, ein elektrisches Feld, das Löcher anzieht, wodurch sie von der Quelle zum Abfluss fließen und so die Stromleitung ermöglichen.

Kontrolle eines P-Kanal-JFET: Aktivierung und Deaktivierung

Abbildung 11: P-Kanal-JFET-Symbol

Durch die Aktivierung eines P-Kanal-JFET muss eine positive Spannung auf den Quellklett angewendet werden, während das Gate-Terminal bei 0 V beibehalten wird.Diese Konfiguration erstellt ein elektrisches Feld, das die Bewegung von Löchern (die Mehrheitsträger in einem P-Kanal-JFET) durch den Kanal erleichtert, was zu einem maximalen Stromfluss von der Quelle zum Abfluss führt.Umgekehrt wird ein N-Kanal-JFET mit Elektronen als Mehrheitsträger aktiviert, indem eine positive Spannung auf den Abfluss angewendet wird, während das Tor bei 0 V bleibt.

Um einen P-Kanal-JFET zu deaktivieren, schneiden Sie entweder die positive Spannung an der Quelle ab oder wenden Sie eine positive Spannung auf das Tor an.Das Entfernen der Quellspannung hält die Antriebskraft für den Stromfluss an und schaltet das Gerät effektiv aus.Alternativ erhöht die Anwendung einer positiven Gate-Spannung die umgekehrte Vorspannung an der P-N-Verbindung von Gate-Source, wodurch der Abbaubereich innerhalb des Kanals erweitert wird.Dies reduziert den Lochfluss und verringert die Leitfähigkeit des Kanals, bis der Stromfluss vollständig stoppt.Für ein N-Kanal-JFET erreicht die Anwendung einer negativen Gate-Spannung eine Deaktivierung und bietet eine präzise Kontrolle über das JFET, was für Anwendungen, die eine feiner Stromregulation benötigen, wie z.

Konstruktions- und Betriebsprinzip eines P-Kanal-JFET

Abbildung 12: P-Kanal-Jfet-Grundstruktur

Die Konstruktion eines P-Kanal-JFET umfasst ein P-Typ-Halbleiter-Substrat, der den Hauptkanal für den Lochfluss bildet.Dieses Substrat ist leicht mit Akzeptorverunreinigungen wie Bor dotiert, um den primären leitenden Pfad für Löcher zu erzeugen, der sich mit dem in N-Kanal-JFETs verwendeten N-Channel-JFETs gegenüberstellt.Der P-Typ-Kanal ermöglicht es Löchern, sich von der Quelle in den Abfluss zu bewegen, der durch eine angelegte Spannung angetrieben wird.Leichte Doping gewährleistet eine angemessene Leitfähigkeit, während die Kontrolle über den Lochfluss über das Tor aufrechterhalten wird.

An beiden Enden des P-Typs-Kanals bilden stark dotierte P+ -Regionen die Quellen- und Abflussanschlüsse (D), die durch Diffusions- oder Ionenimplantationsprozesse erzeugt werden, was zu hohen Leitfähigkeitsbereichen für eine effiziente Lochinjektion und -erfassung führt.Die Quelle, in der Löcher in den Kanal eintreten, und der Abfluss, in dem sie verlassen, werden durch die Drain-Source-Spannung (V_DS) erleichtert, wodurch niedrige Widerstandspfade gewährleistet sind, die den Stromfluss verbessern.Im Gegensatz dazu verwenden N-Kanal-JFETs stark dotierte N+ -Regionen für den Elektronenfluss.

Die Gate-Regionen in einem P-Kanal-JFET werden gebildet, indem das Materialsubstrat vom P-Typ auf beiden Seiten des Kanals in das P-Typ-Typ diffuse, wodurch P-N-Übergänge zwischen dem Gate und dem P-Typ-Kanal erzeugt werden.Das Tor, das in zwei symmetrische N-Typ-Regionen aufgeteilt wird, die den Kanal flankieren, steuert die Breite und Leitfähigkeit des Kanals durch Anwenden einer Gate-Source-Spannung (V_GS).Dies moduliert die Breite des Depletionsbereichs an der P-N-Verbindung und steuert den Stromfluss zwischen Quelle und Abfluss.Im Gegensatz zum N-Kanal-JFET mit p-Typ-Gate-Regionen und einem N-Typ-Kanal beeinflusst die Gate-Spannung in einem P-Kanal-JFET den Kanal, indem er den Lochfluss abnimmt oder verbessert, was eine präzise Kontrolle über seinen Betrieb bietet.

Eine dünne Isolierschicht aus Siliziumdioxid (SiO₂) wird über die Gate -Regionen gezüchtet, um das Tor elektrisch vom Kanal zu isolieren, um sicherzustellen, dass das Gate die Leitfähigkeit des Kanals nur durch den elektrischen Feldffekt ohne Gleichstromfluss zwischen Gate und Kanal steuert.Diese hohe Eingangsimpedanz ist ein definierendes Merkmal von JFETs, wodurch sie in verschiedenen Anwendungen hocheffizient sind.Dieses Isolierprinzip gilt sowohl für P-Kanal- als auch für N-Kanal-JFETs.

Metallkontakte werden an den Bereichen Quelle, Abfluss und Gate unter Verwendung von Techniken wie Sputter oder Verdunstung abgelagert, wobei typischerweise Aluminium oder andere geeignete Metalle verwendet werden.Photolithographische Methoden werden verwendet, um das Metall genau zu modellieren, um genaue und zuverlässige elektrische Verbindungen zu gewährleisten und den Stromfluss durch die Quelle und den Abfluss zu erleichtern, während die Kontrollspannungen auf das Gate angewendet werden können.

In der symbolischen Darstellung des P-Kanal-JFET steuert das Gate den Stromfluss zwischen dem Abfluss und der Quelle.Das Symbol vermittelt visuell die Beziehung zwischen der Gate-Source-Spannung (V_GS) und dem Drain-Source-Strom (i_ds).Eine positive Gate-Source-Spannung stellt Löcher aus dem Kanal ab, wodurch die Breite der Depletionsregion erhöht und dadurch den Stromfluss durch das Gerät gesteuert wird.Dies steht im Gegensatz zu einem N-Kanal-JFET, bei dem eine negative Spannung der Gate-Source den Elektronenfluss steuert.

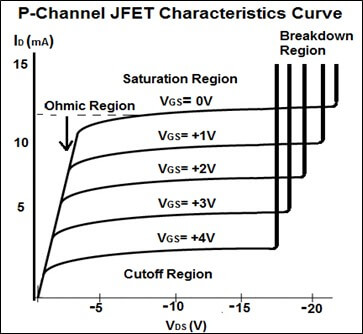

Eigenschaftenkurve eines P-Kanal-JFET

Die Eigenschaftenkurve eines P-Kanal-JFET ist ein wichtiges Instrument, um das Verhalten des Geräts unter verschiedenen elektrischen Bedingungen zu verstehen.Diese Kurve zeigt die Beziehung zwischen dem Abflussstrom (I_D) und der Drain-Source-Spannung (V_DS) für verschiedene Gate-Source-Spannungen (V_GS).Es bietet Einblicke in die Betriebsregionen des JFET und hilft den Ingenieuren, ihre Leistung in elektronischen Schaltungen vorherzusagen und zu manipulieren.Es gibt bemerkenswerte Unterschiede im Vergleich zur Eigenschaftenkurve eines N-Kanal-JFET.

Abbildung 13: P-Kanal-Eigenschaftenkurve

Die charakteristische Kurve hebt verschiedene Regionen hervor: Ohmic, Sättigung, Cutoff und Zusammenbruch.Jede Region repräsentiert eine andere Betriebsart, die Anwendungen wie Verstärkung und Umschaltung unterstützt.

Im ohmischen Bereich arbeitet der JFET wie ein variabler Widerstand, wobei der Abflussstrom (I_D) mit einer Erhöhung der Drain-Source-Spannung (V_DS) für eine bestimmte Gate-Source-Spannung (V_GS) linear zunimmt.Diese lineare Beziehung ist in Anwendungen nützlich, die einen von der Gate -Spannung gesteuerten variablen Widerstand erfordern, was bei analogen Schaltkreisen signifikant ist, die eine präzise Widerstandskontrolle benötigen.Im Gegensatz zum N-Kanal-JFET, in dem diese Region normalerweise mit negativem (V_GS) untersucht wird, benötigt das P-Kanal positiv (V_GS).

Wenn (v_ds) weiter zunimmt, tritt das JFET in den Sättigungsbereich ein, in dem (i_d) relativ konstant und unabhängig von (v_ds) wird.In dieser Region wirkt der JFET als konstante Stromquelle, ideal für die Verstärkung.Die Gate-Source-Spannung (V_GS) steuert die Strommenge über das Gerät und macht diesen Bereich für die Signalverstärkung von Bedeutung.Ingenieure verwenden dieses Merkmal für die Gestaltung stabiler und hoher Verstärker.Im Vergleich zum N-Kanal-JFET wird der Sättigungsbereich in P-Kanal-Geräten mit einem positiven (V_GS) erreicht, wodurch die Konstruktions- und Anwendungsüberlegungen des Geräts beeinflusst werden.

In der Grenzregion erzeugt eine ausreichend positive Gate-Source-Spannung (V_GS) eine starke umgekehrte Vorspannung am Tor, wodurch der Verarmungsbereich erweitert und den Kanal abgeklemmt wird.Der Abflussstrom (I_D) wird vernachlässigbar und schaltet das JFET effektiv aus und wird für Schaltanwendungen verwendet, bei denen eine vollständige Beendigung des Stromflusses erforderlich ist.

In der Breakdown -Region kann bei hohen Werten von (v_ds) der JFET eine Lawinenverletzung erleben, was dazu führt, dass der Abflussstrom schnell zunimmt.Diese Region wird in der Regel im normalen Betrieb vermieden, um die Schädigung der Geräte zu vermeiden.Das Verständnis dieser Region ist erforderlich, um die Zuverlässigkeit und Langlebigkeit von JFET in praktischen Anwendungen sicherzustellen.Die Breakdown-Eigenschaften und Spannungsniveaus können sich aufgrund der intrinsischen Eigenschaften der verwendeten Halbleitermaterialien zwischen P-Kanal- und N-Kanal-JFETs unterscheiden.

Die Transkonduktanz (G_M) eines JFET repräsentiert den Gewinn des Transistors und wird als Steigung der (i_d) gegen (v_gs) Kurve im Sättigungsbereich ausgedrückt.Je höher die Transkonduktanz ist, desto höher ist die Empfindlichkeit gegenüber Änderungen in (V_GS), wodurch das JFET am Gate empfindlicher gegenüber kleinen Spannungsänderungen empfindlicher wird.Diese Eigenschaft ist nützlich in der Verstärkerdesign, bei der eine präzise Steuerung des Ausgangsstroms erforderlich ist.Das Betriebsverhalten des JFET in verschiedenen Regionen unterstreicht seine Vielseitigkeit und Anpassungsfähigkeit in einer Vielzahl elektronischer Anwendungen.Sowohl für P-Kanal- als auch für N-Kanal-JFETs spielt die Transkonduktanz trotz der unterschiedlichen Kontrollspannungspolaritäten eine Schlüsselrolle.

In praktischer Hinsicht wird ein P-Kanal-JFET betrieben, um das Gerät in der gewünschten Region sorgfältig auszuwählen (V_GS).Die ohmische Region wird für lineare Anwendungen, die Sättigungsregion für die Verstärkung und den Grenzbereich zum Schalten bevorzugt, um sicherzustellen, dass das JFET vollständig ausgeschaltet ist.Der Einfluss von (v_gs) auf (i_d) ist signifikant, da verschiedene (v_gs) -Werte den Betriebspunkt des Geräts verschieben.

|

Merkmale |

N-Kanal FET |

P-Kanal-Fet |

|

Aufladung Träger |

Elektronen |

Löcher |

|

Mehrheitlich Träger |

Elektronen |

Löcher |

|

Leitfähigkeit |

Führt wann VGS ist positiv |

Führt wann VGS ist negativ |

|

Anmachen Stromspannung |

Positiv |

Negativ |

|

Umschalten Geschwindigkeit |

Schneller |

Langsamer |

|

Strömungsrichtung abtropfen lassen |

Von Abfluss zur Quelle |

Von der Quelle zum Abtropfen |

|

Stromspannung Handhabung |

Typischerweise Wird für positive Spannungsanwendungen verwendet |

Typischerweise Wird für negative Spannungsanwendungen verwendet |

|

Tor Grenzspannung |

Typischerweise hat eine niedrigere (negative) Gate -Schwellenspannung |

Typischerweise hat eine höhere (positive) Gate -Schwellenspannung |

|

Kosten |

Allgemein untere |

Allgemein höher |

|

Hitze Dissipation |

Weniger Hitze Dissipation aufgrund des Mehrheitsunternehmens sind Elektronen |

Mehr Wärme Dissipation aufgrund des Mehrheitsunternehmens, das Löcher ist |

|

Lärm Empfindlichkeit |

Weniger geräuschempfindlich |

Mehr geräuschempfindlich |

Diagramm 1: N-Kanal JFET gegen P-Kanal JFET

Abschluss

Das Verständnis der Konstruktion und Funktionalität von FETs ermöglicht es Designern, sie effektiv in verschiedenen Anwendungen zu implementieren und die Leistung und Effizienz elektronischer Systeme zu verbessern.Die hohe Eingangsimpedanz von FETs sorgt für eine minimale Belastung in den vorhergehenden Stadien und macht sie ideal für Verstärker und andere Signalverarbeitungsschaltungen.Darüber hinaus ist der geringe Stromverbrauch von FETs bei batteriebetriebenen Geräten und leistungsempfindlichen Anwendungen vorteilhaft.

FETs mit ihren einzigartigen Eigenschaften und vielseitigen Anwendungen sind weiterhin unverzichtbare Komponenten in der Entwicklung der modernen Elektronik.Dieser Artikel hat einen umfassenden Überblick über JFETs gegeben, in dem die Schlüsselkomponenten, betrieblichen Prinzipien und Anwendungen hervorgehoben werden, wodurch Designer diese Geräte in ihren elektronischen Designs effektiv nutzen können.Durch die Beherrschung der Feinheiten von FETs können Designer zu erheblichen Fortschritten in elektronischen Systemen beitragen und sowohl die Funktionalität als auch die Effizienz in einer Vielzahl von Anwendungen verbessern.

Häufig gestellte Fragen [FAQ]

1. Was sind die wichtigsten Parameter bei der Auswahl eines JFET für eine bestimmte Anwendung?

Bei der Auswahl eines JFET für eine bestimmte Anwendung sollten mehrere wichtige Parameter bewertet werden, um eine optimale Leistung zu gewährleisten.Zunächst misst Transkonduktanz (GM) die Effizienz der Umwandlung von Änderungen der Gate -Spannung in Variationen des Abflussstroms;Eine höhere Transkonduktanz zeigt eine bessere Leistung für die Verstärkung an.Zweitens ist die Drain-Source-Sättigungsspannung (VDS) die minimale Spannung, die an den Ablaufanschlüssen erforderlich ist, damit der JFET im Sättigungsmodus betrieben wird, was für eine effektive Verstärkung von Bedeutung ist.Drittens ist die Gate -Schwellenspannung (VTH) die minimale Gate -Spannung, die erforderlich ist, um einen leitenden Pfad zwischen Quelle und Abfluss zu erzeugen, der die Schalteigenschaften des JFET beeinflusst.Zuletzt ist On-Resistenance (RDS (ON)) der Widerstand zwischen Abfluss und Quelle, wenn sich das JFET vollständig eingeschaltet hat.Niedrigere Werte für die Resistenz verbessern die Leistungseffizienz durch Reduzierung des Stromverlusts.

2. Wie wirkt sich die Temperatur auf die Leistung von JFETs aus?

Die Temperatur beeinflusst die JFET -Leistung erheblich, indem sie ihre elektrischen Eigenschaften verändert.Mit zunehmendem Temperatur steigt die Intrinsischen Trägerkonzentration im Halbleitermaterial, was zu höheren Leckströmen und einer verringerten Schwellenspannung führt.Diese Reduzierung kann dazu führen, dass das JFET an den unteren Gate -Spannungen eingeschaltet wird, wodurch die Schaltung möglicherweise destabilisiert wird.Zusätzlich beeinflussen Temperaturänderungen die Transkonditionanz (GM) und die On-Resistenz (RDS (ON)) und beeinflussen die Effizienz des JFET bei Verstärkung und Umschaltung.Ein wirksames thermisches Management, einschließlich Kühlkörper und ordnungsgemäßer Belüftung, ist sehr wichtig, um diese Effekte zu mildern und eine konsistente Leistung aufrechtzuerhalten.

3. Was sind die Vorteile der Verwendung von JFETs gegenüber BJTs in bestimmten Anwendungen?

JFETs bieten in bestimmten Anwendungen mehrere Vorteile gegenüber bipolaren Junction -Transistoren (BJTs).JFETs haben eine hohe Eingangsimpedanz, die den Belastungseffekt auf die vorhergehenden Stufen minimiert und sie ideal für Eingangsstadien von Verstärkern und hochwertigen Anwendungen ideal machen.Sie erzeugen weniger Rauschen als BJTs, was für die Signalverstärkung auf niedriger Ebene in Audio- und HF-Schaltungen vorteilhaft ist.JFETs weisen typischerweise auch eine bessere thermische Stabilität auf und verbrauchen weniger Leistung, sodass sie für batteriebetriebene und tragbare Geräte geeignet sind.Diese Eigenschaften machen JFETs vorzuziehen, wenn Signalintegrität, Leistungseffizienz und thermische Stabilität erforderlich sind.

4. Was sind die typischen Fehlermodi von JFETs und wie können sie verhindert werden?

JFETs können aufgrund eines thermischen Ausreißers, des Aufschlusses von Gateoxid und einer Lawinenverletzung scheitern.Thermischer Ausreißer tritt auf, wenn eine übermäßige Wärme dazu führt, dass das JFET mehr Strom leitet, mehr Wärme erzeugt und möglicherweise zu einem Versagen führt.Verhindern Sie dies, indem Sie ein wirksames thermisches Management wie Kühlkörper und ordnungsgemäße Kühlung verwenden.Die Aufschlüsselung des Gateoxids tritt auf, wenn die übermäßige Spannung über den Gate-Source-Übergang die Isolierschicht schädigt und zu Leckageströmen oder einem Ausfall des Geräts führt.Spannungsklemme und Begrenzungsschaltungen können sich dagegen schützen.Der Durchbruch der Avalanche tritt auf, wenn die Drain-Source-Spannung den maximalen Nennwert überschreitet, was zu einem plötzlichen Strom erhöht wird, der das Gerät beschädigen kann.Vermeiden Sie dies, indem Sie Schaltungen innerhalb der Spannungsbewertungen des JFET und verwenden und verwenden Sie Schutzmaße wie transiente Spannungssuppressoren.

5. Wie beeinflusst die Eingangsimpedanz eines JFET seine Anwendung in elektronischen Schaltungen?

Die hohe Eingangsimpedanz eines JFET ist in verschiedenen elektronischen Schaltkreisen ein signifikanter Vorteil.Dies bedeutet, dass das JFET einen minimalen Strom aus der vorhergehenden Stufe zeichnet, wodurch der Belastungseffekt verringert und die Integrität des Eingangssignals erhalten bleibt.Dies ist besonders bei Verstärkerschaltungen von Vorteil, bei denen die Aufrechterhaltung der Signaltreue sehr wichtig ist.In Pufferschaltungen ermöglicht die hohe Eingangsimpedanz, dass das JFET als effektive Schnittstelle zwischen hohen Impedanzquellen und Lasten mit niedriger Impedanz fungiert, um eine effiziente Signalübertragung sicherzustellen.Eine hohe Eingangsimpedanz macht JFETs auch für empfindliche Messinstrumente geeignet, wobei die Auswirkungen auf das gemessene Signal erforderlich sind.Insgesamt verbessert eine hohe Eingangsimpedanz die Vielseitigkeit und Effektivität von JFETs in vielen elektronischen Anwendungen.

Verwandter Artikel

-

Jun 25 2024Die vollständige Anleitung zur Wärmepaste für elektronische Komponenten

Jun 25 2024Die vollständige Anleitung zur Wärmepaste für elektronische KomponentenThermische Paste spielt eine Schlüsselrolle bei der Aufrechterhaltung der Effizienz und Langlebigkeit von Wärmegenerierungskomponenten wie CPUs und ... -

Jun 21 2024Universelle Gates: Die Grundlagen des zeitgenössischen digitalen Logikdesigns

Jun 21 2024Universelle Gates: Die Grundlagen des zeitgenössischen digitalen LogikdesignsEntdecken Sie die transformativen Auswirkungen von universellen Toren in der digitalen Elektronik, indem Sie unseren eingehenden Artikel über NAND un...

Verwandte -Produkte

LMV654MT/NOPB

IC OPAMP GP 4 CIRCUIT 14TSSOP

RT0805BRE075K9L

RES SMD 5.9K OHM 0.1% 1/8W 0805

PIC16LF1824T-I/ML

IC MCU 8BIT 7KB FLASH 16QFN

HEDS-5500#A14

ROTARY ENCODER OPTICAL 500PPR

PIC18LF26K22-I/ML

IC MCU 8BIT 64KB FLASH 28QFN

MBM29F040C-70PD

MBM29F040C-70PD FUJITSU

AM29LV400BB-90EC

AM29LV400BB-90EC AMD

ABA-54563

ABA-54563 AVAGO

HSP50210JI-52

DIGITAL COSTAS LOOP

TMP86F549BFG

TMP QFP

FS32K144UFT0VLL

FREESCAL QFP100

M7586-01T

OKI TQFP